### ΠΑΝΕΠΙΣΤΗΜΙΟ ΙΩΑΝΝΙΝΩΝ ΣΧΟΛΗ ΘΕΤΙΚΩΝ ΕΠΙΣΤΗΜΩΝ ΤΜΗΜΑ ΦΥΣΙΚΗΣ

# Αναβαθμίσεις του Συστήματος Σκανδαλισμού Μιονίων στην Κυλινδρική Περιοχή του Πειράματος CMS στο CERN για τον LHC και τον HL-LHC

Σταύρος Μάλλιος

ΔΙΔΑΚΤΟΡΙΚΗ ΔΙΑΤΡΙΒΗ

ΙΩΑΝΝΙΝΑ 2019

# The CMS Barrel Muon Track Finder and Upgrades for HL-LHC

Stavros Mallios

**DOCTORAL THESIS**

**IOANNINA 2019**

### **Three-member Advisory Committee**

- 1. Ioannis Papadopoulos, Assistant Professor, Department of Physics, University of Ioannina, Greece (Thesis Supervisor).

- 2. Konstantinos Fountas, Professor, Department of Physics, University of Ioannina, Greece.

- 3. Ioannis Evangelou, Associate Professor, Department of Physics, University of Ioannina, Greece.

#### Seven-member Assessment Committee

- 1. Ioannis Papadopoulos, Assistant Professor, Department of Physics, University of Ioannina, Greece (Thesis Supervisor).

- 2. Konstantinos Fountas, Professor, Department of Physics, University of Ioannina, Greece.

- 3. Ioannis Evangelou, Associate Professor, Department of Physics, University of Ioannina, Greece.

- 4. Nikolaos Manthos, Associate Professor, Department of Physics, University of Ioannina, Greece.

- 5. Vasilios Christofilakis, Assistant Professor, Department of Physics, University of Ioannina, Greece.

- 6. Dimitrios Loukas, Director of Research, Democritus Institute of Nuclear and Particle Physics (INPP).

- 7. Michalis Bachtis, Assistant Professor, Department of Physics & Astronomy, UCLA, USA.

# Acknowledgments

Firstly, I would like to thank all the members of High-Energy Physics Laboratory (HEPLAB) and especially my supervisor Assistant Professor I. Papadopoulos. His guidance and support helped me during the time of research and writing of this thesis. I would also like to express my sincere gratitude to my advisor and mentor Professor K. Fountas for his patience, motivation, and immense knowledge. I could not have imagined having better mentor for my Ph.D study.

Special thanks to M. Bachtis for our amazing collaboration without which, this thesis would not be possible, and K. Velidis for his immense support and excellent life and career advises.

I thank my fellow lab-mates and friends G. Flouris, V. Paradas, P. Katsoulis and G. Karathanasis for the stimulating discussions, for the sleepless nights we were working together before deadlines, and for all the fun we have had in the last four years.

I gratefully thank Greg Iles for enlightening and advising me, and all the UK-CMS trigger group for their support in the use of the MP7 and Serenity cards. I am grateful to my colleagues and friends S. A. Thayil, Antonis Agapitos and Sarah Freed, for all the psychological support and for their valuable contribution in the process of writing and editing the present dissertation.

Last but not least, I would like to thank my family and especially my mother Athina, for supporting me throughout writing this thesis and my life in general.

### **Abstract**

The Compact Muon Solenoid (CMS) is a general purpose experiment measuring proton-proton and heavy-ion collisions at the Large Hadron Collider (LHC) at CERN. The LHC is a large particle accelerator at the CERN research laboratory, designed to provide particle physics experiments with collisions at unprecedented centre-of-mass energies. To extend the sensitivity for new physics searches, a major upgrade of the LHC has been decided and is being prepared, the High Luminosity LHC (HL-LHC). In its "ultimate" configuration, the HL-LHC would reach a peak instantaneous luminosity of  $7-7.5\times10^{34}~{\rm cm}^{-2}{\rm s}^{-1}$  increasing the "pile-up" or the average number of proton-proton collisions per bunch crossing to around 200. In order to maintain the excellent performance, the CMS detector has planned a complete replacement of the trigger electronics and a full redesign of the system's architecture.

In this dissertation, the contributions to the Phase-2 CMS detector upgrade are presented, comprised of the design and testing of a new high-speed link protocol for the Phase-2 trigger, the integration of a new muon tracking algorithm for the Barrel Muon Trigger in the Barrel Muon Trigger boards and the contribution in the design and testing of a demonstrator board for the Layer-1 Barrel Muon Trigger. The new links takes advantage of all the latest advances in technology to increase the bandwidth of the trigger channels to 16 Gbps and 25 Gbps. The new muon tracking algorithm is featuring a Kalman filter and extends the trigger capabilities in finding displaced muons originating from very long lived particles. The efficiency of tracking such muons, originating 40 cm to 100 cm away from the interaction vertex, is increased by a factor of 2.5. Finally, the new demonstrator board, features a 20 nm technology Field Programmable Gate Array (FPGA) and it is capable of running sixteen optical links at 16 Gbps, with excellent Bit Error Ratio (BER) of less than  $10^{-15}$ .

# **Contents**

| 1                           | Introduction |                                     |    |  |  |

|-----------------------------|--------------|-------------------------------------|----|--|--|

| 2 The Large Hadron Collider |              |                                     |    |  |  |

|                             | 2.1          | The LHC injector chain              | 31 |  |  |

|                             | 2.2          | Luminocity of the LHC               | 33 |  |  |

|                             | 2.3          | LHC experiments                     | 35 |  |  |

|                             | 2.4          | The High Luminocity LHC upgrade     | 37 |  |  |

|                             |              | 2.4.1 The HL-LHC luminocity         | 38 |  |  |

| 3                           | The          | CMS experiment                      | 41 |  |  |

|                             | 3.1          | The CMS Coordinate system           | 43 |  |  |

|                             | 3.2          | The superconducting solenoid magnet | 43 |  |  |

|                             | 3.3          | The Inner Tracking System Overview  | 46 |  |  |

|                             |              | 3.3.1 The Silicon Strip Tracker     | 46 |  |  |

|                             |              | 3.3.2 The Pixel Detector            | 47 |  |  |

|                             | 3.4          | The Electromagnetic Calorimeter     | 49 |  |  |

|                             | 3.5          | The Hadronic Calorimeter            | 52 |  |  |

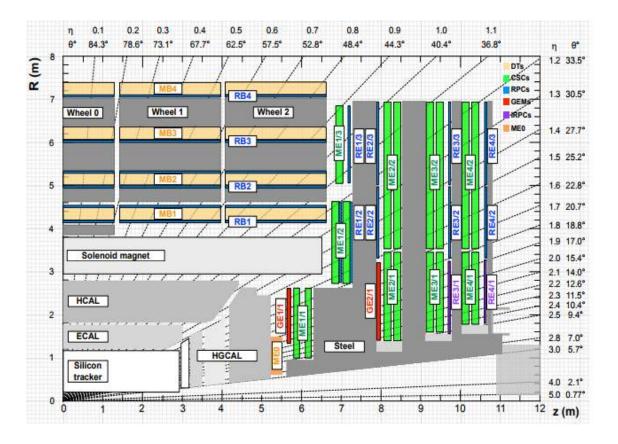

|   | 3.6  | The muon system                                               | 53 |

|---|------|---------------------------------------------------------------|----|

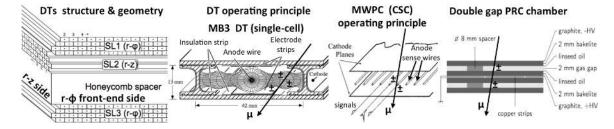

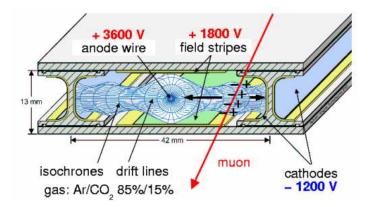

|   |      | 3.6.1 The Drift Tube system                                   | 54 |

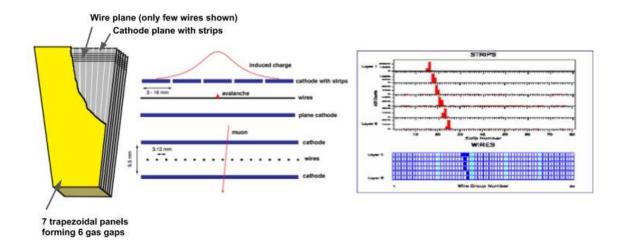

|   |      | 3.6.2 The Cathode Strip Chambers                              | 56 |

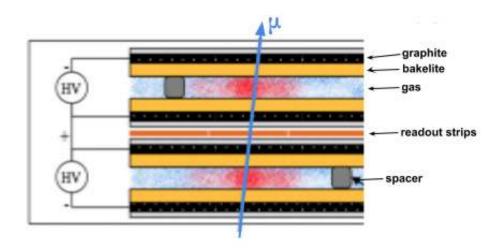

|   |      | 3.6.3 The Resistive Plate Chambers                            | 57 |

|   |      | 3.6.4 CMS muon system upgrades for the HL-LHC                 | 58 |

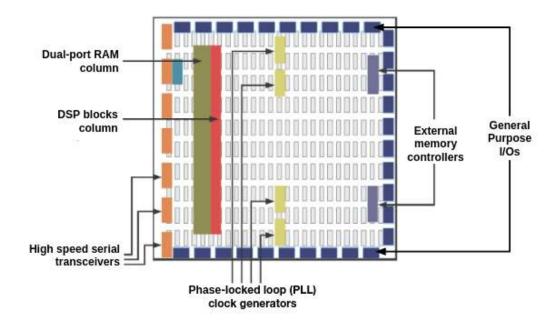

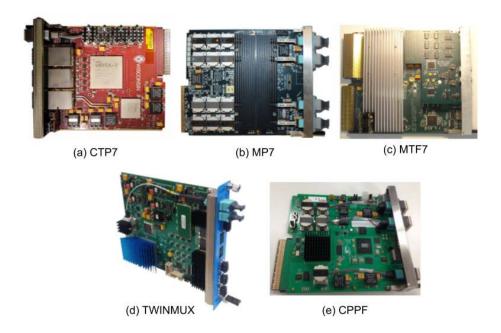

| 4 | Tech | nnology and electronics                                       | 61 |

|   | 4.1  | Introduction                                                  | 61 |

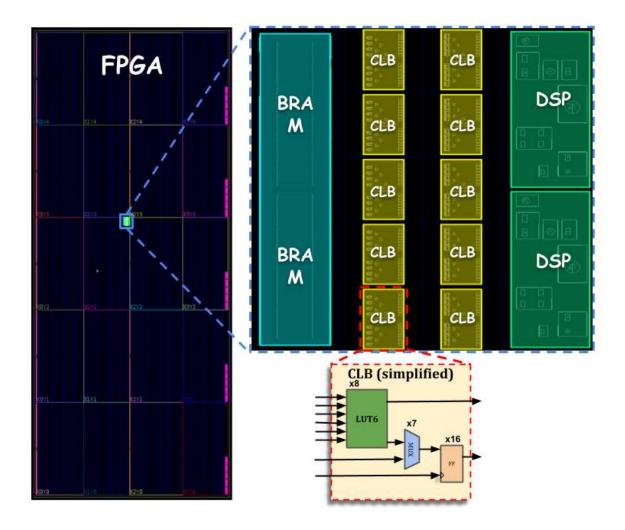

|   | 4.2  | Field-Programmable Gate Arrays                                | 61 |

|   |      | 4.2.1 Contemporary FPGA Architecture                          | 62 |

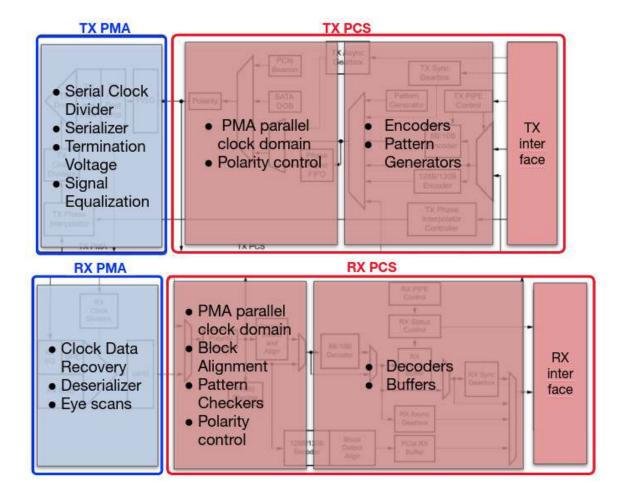

|   |      | 4.2.2 Multi-Gigabit Transceivers                              | 63 |

|   |      | 4.2.3 FPGAs compared to other Programmable Logic technologies | 66 |

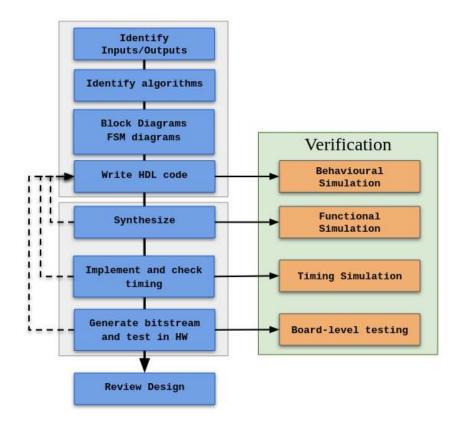

|   | 4.3  | Hardware Description Languages                                | 67 |

|   |      | 4.3.1 Overview                                                | 67 |

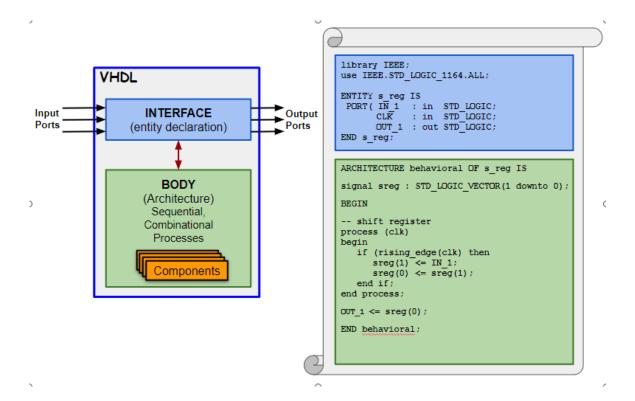

|   |      | 4.3.2 VHDL                                                    | 69 |

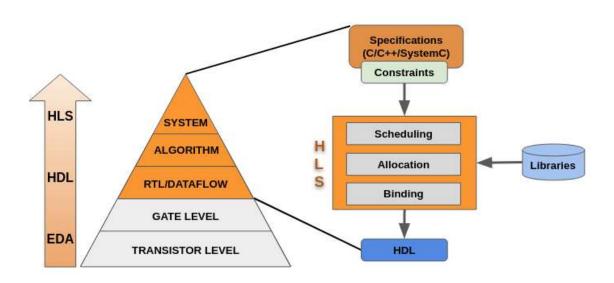

|   |      | 4.3.3 High Level Synthesis                                    | 70 |

| 5 | The  | CMS Trigger System                                            | 73 |

|   | 5.1  | The Level-1 Trigger                                           | 73 |

|   | 5.2  | The Level-1 Trigger upgrade for Run 2                         | 75 |

|   |      | 5.2.1 Architecture and Hardware upgrades                      | 76 |

|   | 5.3  | The Calorimeter Trigger                                       | 80 |

|   |      | 5.3.1 The Calorimeter Trigger Layer-1                         | 80 |

|   |      | 5.3.2    | The Calorimeter Trigger Layer-2                                    | 82  |

|---|------|----------|--------------------------------------------------------------------|-----|

|   | 5.4  | The M    | uon Trigger                                                        | 83  |

|   |      | 5.4.1    | The Barrel Muon Trigger                                            | 85  |

|   |      | 5.4.2    | The Endcap Muon Trigger                                            | 87  |

|   |      | 5.4.3    | The Overlap Muon Trigger                                           | 88  |

|   |      | 5.4.4    | The Global Muon Trigger                                            | 89  |

|   | 5.5  | The Gl   | obal Trigger                                                       | 90  |

|   | 5.6  | The Hi   | gh Level Trigger                                                   | 93  |

|   | 5.7  | The Le   | vel-1 Muon Trigger for Phase-2                                     | 94  |

| 6 | The  | Rarral l | Muon Track finder System and upgrades                              | 97  |

| U | IIIC | Darrer   | vition Track index system and upgrades                             | )   |

|   | 6.1  | The leg  | gacy Barrel Muon Track Finder algorithm                            | 97  |

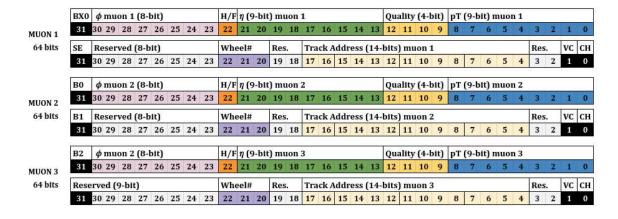

|   |      | 6.1.1    | BMTF inputs and deserializer units                                 | 98  |

|   |      | 6.1.2    | The Phi Track Finder (PHTF)                                        | 99  |

|   |      | 6.1.3    | The Eta Track Finder (ETTF)                                        | 103 |

|   |      | 6.1.4    | The Wedge Sorter (WS)                                              | 105 |

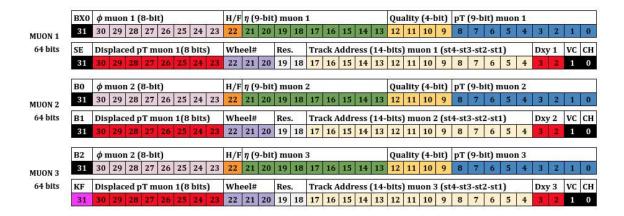

|   |      | 6.1.5    | Serialization and BMTF outputs format                              | 106 |

|   | 6.2  | A Kalr   | nan Filter algorithm for the Barrel Muon Track Finder              | 106 |

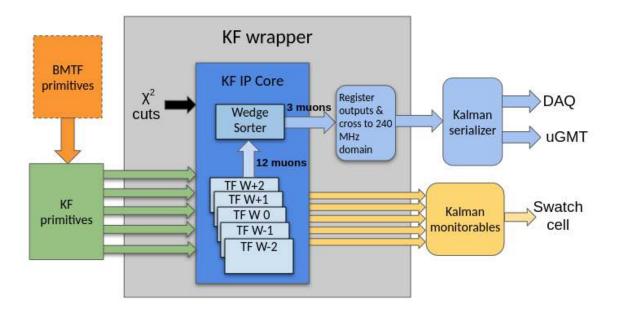

|   |      | 6.2.1    | The new Kalman filter algorithm                                    | 107 |

|   |      | 6.2.2    | The Kalman filter firmware                                         | 109 |

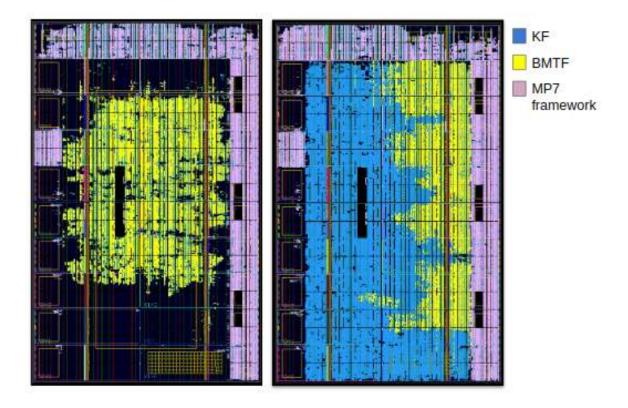

|   |      | 6.2.3    | Parallel Implementation of the legacy and Kalman filter algorithms | 110 |

|   |      | 6.2.4    | Area and Latency considerations                                    | 111 |

|   |      | 6.2.5    | Interface and timing considerations                                | 113 |

|   |      |          |                                                                    |     |

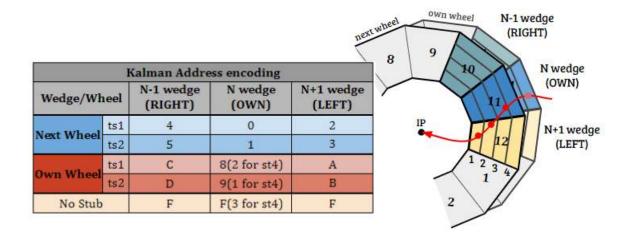

|   |     | 6.2.6   | Kalman filter inputs                                                             | 115 |

|---|-----|---------|----------------------------------------------------------------------------------|-----|

|   |     | 6.2.7   | Kalman Filter outputs                                                            | 116 |

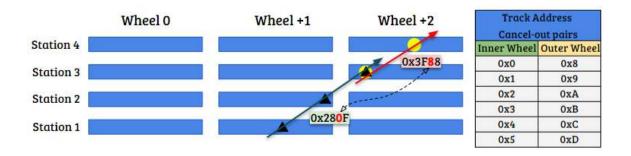

|   |     | 6.2.8   | The Kalman filter cancel-out logic in the uGMT                                   | 117 |

|   |     | 6.2.9   | Firmware - Emulator comparisons                                                  | 118 |

|   |     | 6.2.10  | Efficiency and rate of the new algorithm                                         | 119 |

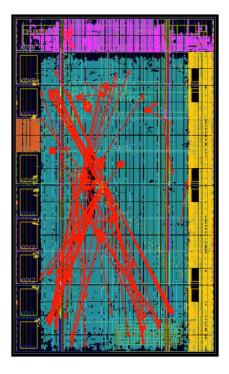

|   | 6.3 | A dem   | onstrator board for the Phase-2 Layer 1 Barrel Muon Trigger                      | 121 |

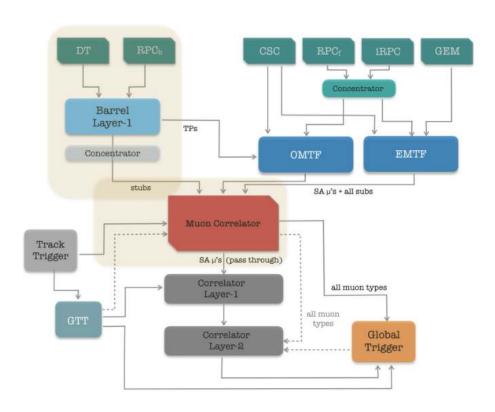

|   |     | 6.3.1   | Architecture of the Barrel Muon Trigger System for Phase 2                       | 121 |

|   |     | 6.3.2   | The hardware                                                                     | 123 |

|   |     | 6.3.3   | Debugging and testing of the optical links                                       | 126 |

|   |     |         |                                                                                  |     |

| 7 | Her | mes: A  | high speed link protocol for the HL-LHC CMS experiment                           | 129 |

|   | 7.1 | Introdu | action                                                                           | 129 |

|   | 7.2 | The 10  | Gbps asynchronous link protocol for the Phase-1 CMS trigger system $ . $ . $ . $ | 130 |

|   | 7.3 | Link re | equirements for the Phase-2 CMS trigger system                                   | 131 |

|   | 7.4 | The He  | ermes asynchronous link protocol for the Phase-2 CMS trigger system              | 133 |

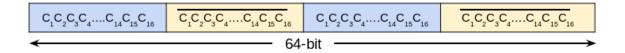

|   |     | 7.4.1   | The 64b66b encoding                                                              | 133 |

|   |     | 7.4.2   | The Aurora protocol                                                              | 135 |

|   |     | 7.4.3   | Overview of the <i>Hermes</i> protocol                                           | 138 |

|   |     | 7.4.4   | The protocol interface                                                           | 138 |

|   |     | 7.4.5   | Data Sources                                                                     | 144 |

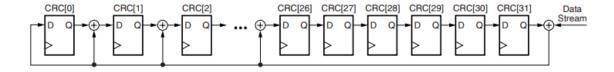

|   |     | 7.4.6   | Error Control - The Cyclic Redundancy Check generator and checker                | 147 |

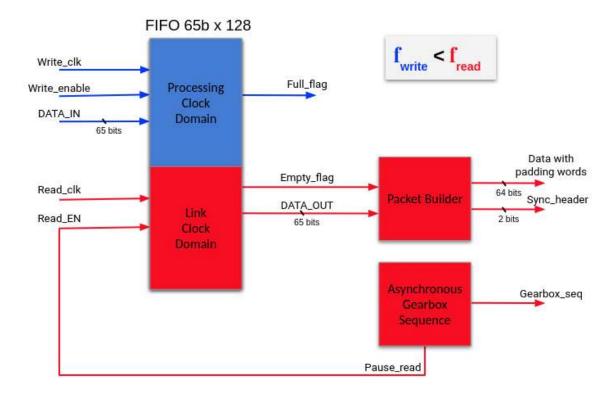

|   |     | 7.4.7   | Crossing from the Processing clock domain to the Link clock domain               | 149 |

|   |     | 7.4.8   | The Packet Builder                                                               | 152 |

|   |     |         |                                                                                  |     |

|   |                 | 7.4.9                       | Initialization                                                     | 154               |

|---|-----------------|-----------------------------|--------------------------------------------------------------------|-------------------|

|   |                 | 7.4.10                      | Auto-link recovery                                                 | 156               |

|   |                 | 7.4.11                      | Crossing from the Link clock domain to the Processing clock domain | 156               |

|   |                 | 7.4.12                      | CRC checksum error detection                                       | 158               |

|   |                 | 7.4.13                      | The ONE_WORD simple link protocol                                  | 158               |

|   | 7.5             | Design                      | Verification and Tests                                             | 159               |

|   |                 | 7.5.1                       | Latency measurements                                               | 160               |

|   |                 | 7.5.2                       | Bit Error Ratio measurements                                       | 162               |

|   |                 |                             |                                                                    |                   |

| 8 | Con             | clusions                    |                                                                    | 165               |

|   |                 |                             | : HDL code                                                         | 165<br>187        |

|   |                 | endix A                     |                                                                    |                   |

|   | Арр             | endix A<br>Herme            | : HDL code                                                         | 187               |

|   | App A.1 A.2     | endix A  Herme  Herme       | : HDL code s protocol frame generator code                         | <b>187</b>        |

|   | App A.1 A.2 A.3 | endix A  Herme  Herme  uGMT | : HDL code s protocol frame generator code                         | 187<br>187<br>190 |

# Εκτεταμένη σύνοψη στα Ελληνικά

### Εισαγωγή

Ο Μεγάλος Επιταχυντής Συγκρουόμενων Δεσμών Πρωτονίων (LHC), βρίσκεται στο ευρωπαϊκό κέντρο πυρηνικών ερευνών CERN, και αποτελεί τον μεγαλύτερο και ισχυρότερο επιταχυντή σωματιδίων στον κόσμο. Αποτελείται από μία διάταξη υπεραγώγιμων μαγνητών μήκους 27 χιλιομέτρων. Ο LHC επιταχύνει δέσμες πρωτονίων ή ιόντων που κινούνται μέσα στον δακτύλιο σε αντίθετες κατευθύνσεις, με ταχύτητες που πλησιάζουν την ταχύτητα του φωτός (99.9999991% c). Οι δέσμες συγκρούονται σε τέσσερα σημεία του δακτυλίου. Γύρω από κάθε σημείο σύγκρουσης, έχουν εγκατασταθεί διατάξεις ανιχνευτών, που αποτελούν τα τέσσερα κύρια πειράματα: CMS, ATLAS, LHCb και ALICE.

Το πείραμα CMS, στο οποίο εκπονήθηκε η παρούσα διατριβή, προκύπτει ως αρκτικόλεξο του "Compact Muon Solenoid", που μεταφράζεται ως Συμπαγές Μιονικό Σωληνοειδές, και αποτελεί έναν από τους δύο μεγάλους ανιχνευτές γενικού σκοπού που λειτουργούν στον LHC.

Οι κυριότεροι στόχοι του CMS είναι η επιβεβαίωση θεωρητικών προβλέψεων του Καθιερωμένου Προτύπου, όπως η ανακάλυψη του μποζονίου Higgs (στόχος που επιτεύχθηκε το 2012), η εξερεύνηση της φυσικής στην κλίμακα των TeV, καθώς και η αναζήτηση φυσικής πέρα από το Καθιερωμένο Πρότυπο, όπως π.χ. η υπερσυμμετρία. Επίσης, το CMS μελετά το πλάσμα κουάρκ και γλουονίων μέσω συγκρούσεων βαρέων ιόντων (Pb σε Pb). Μεγαλύτερη έμφαση έχει δοθεί στη μελέτη των ιδιοτήτων του μποζονίου Higgs, λόγω του βασικού του ρόλου στην κατανόηση της φύσης του σπασίματος της ηλεκτρασθενούς συμμετρίας.

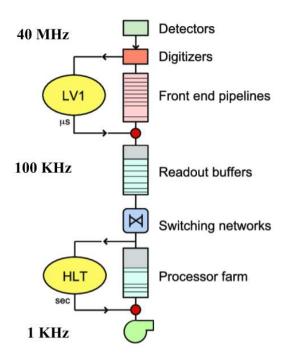

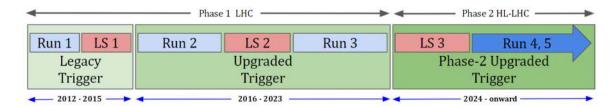

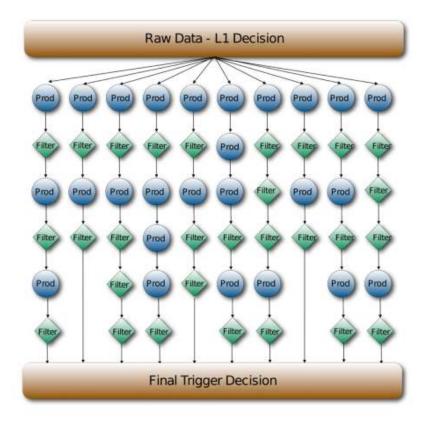

Κατά τη διάρκεια της πρώτης Φάσης (Phase-1) του προγράμματος του LHC (2011-2023), η φωτεινότητα αλληλεπιδράσεων έφτασε τα  $2\times 10^{34}~cm^{-2}s^{-1}$ . Για κάθε αλληλεπίδραση, οι επιμέρους ανιχνευτές του πειράματος CMS παράγουν τεράστιο όγκο πληροφορίας, που υπερβαίνει τα 27 Petabits ανά δευτερόλεπτο, όγκος που είναι αδύνατον να αποθηκευτεί. Μεγάλο μέρος, όμως, της πληροφορίας αυτής, είτε είναι θόρυβος ή δεν προσφέρει κάτι νέο ή χρήσιμο στην Φυσική. Για αυτό τον λόγο, έχει κατασκευαστεί ένα εξελιγμένο ηλεκτρονικό σύστημα επιλογής (σύστημα σκανδαλισμού), υπεύθυνο για τη μείωση του παραγόμενου όγκου δεδομένων κατά 40000 φορές. Η μείωση πραγματοποιείται σε δύο στάδια. Το 10 επίπεδο σκανδαλισμού, ή Level-1 Trigger (L1T), και το δεύτερο επίπεδο σκανδαλισμού ή High Level Trigger (HLT). Το L1T,

αποτελείται από ειδικά σχεδιασμένες ηλεκτρονικές διατάξεις, οι οποίες πρέπει να αποφασίσουν, σε χρόνο μικρότερο των 4 μs, αν θα απορρίψουν την πληροφορία που συλλέχτηκε ή αν θα την αποδώσουν στο δεύτερο επίπεδο σκανδαλισμού για περαιτέρω επεξεργασία. Λαμβάνει δεδομένα από τα καλορίμετρα και από το σύστημα μιονίων, με συχνότητα 40 MHz (εκατομμυρίων γεγονότων ανά δευτερόλεπτο), και επιλέγει 100000 από αυτά (μείωση του ρυθμού στα 100 kHz). Το HLT από την άλλη πλευρά, διαβάζει και επεξεργάζεται την πληροφορία που προέρχεται από το L1T, στην συστοιχία των υπολογιστών του, και επιλέγει τα γεγονότα που ικανοποιούν συγκεκριμένους κανόνες σκανδαλισμού που κάθε φορά τίθενται, ανάλογα με το εκάστοτε μελετώμενο κανάλι φυσικής. Το HLT επιλέγει τις 1000 πιο ενδιαφέρουσες αλληλεπιδράσεις ανά δευτερόλεπτο, οδηγώντας σε τελική μείωση του ρυθμού στο 1 kHz.

Το 2023, ο επιταχυντής LHC πρόκειται να αναβαθμιστεί, και θα εισέλθει στην δεύτερη Φάση του (Phase-2). Ο αναβαθμισμένος LHC, ή High Luminosity LHC (HL-LHC) όπως ονομάζεται, έχει στόχο την διεύρυνση των δυνατοτήτων του επιταχυντή με την φωτεινότητα (luminosity) να φτάνει τα  $7.5 \times 10^{34}~cm^{-2}s^{-1}$ , 7.5 φορές μεγαλύτερη από τον αρχικό σχεδιασμό του επιταχυντή (εικόνα 1). Η αύξηση της φωτεινότητας θα οδηγήσει σε αύξηση τον αριθμό των ταυτοχρόνων συγκρούσεων (pile-up), κατά την σύγκρουση δύο πακέτων πρωτονίων (bunches), από  $\sim 45$  (Φάση I) σε  $\sim 200$ . Το νέο περιβάλλον συγκρούσεων θα απαιτεί μεγαλύτερη αποδοτικότητα των ηλεκτρονικών συστημάτων (efficiency), καλύτερη αξιοπιστία του υλικού και μείωση του ρυθμού σκανδαλισμού (trigger rate).

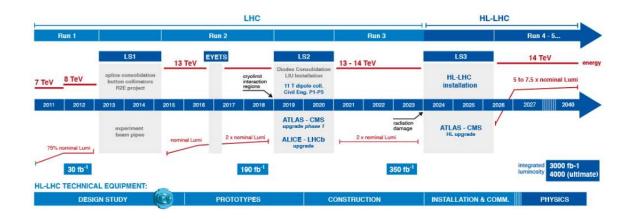

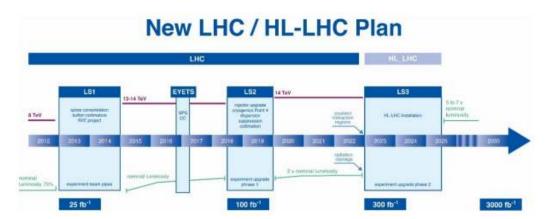

Εικόνα 1: Το χρονοδιάγραμμα της αναβάθμισης του LHC.

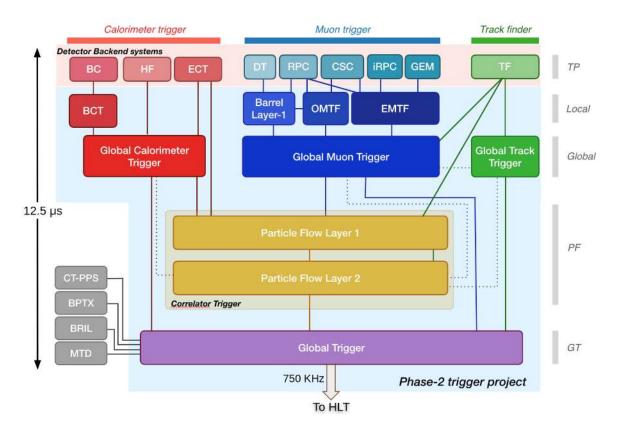

Το πείραμα CMS θα προχωρήσει στην αναβάθμιση τόσο των επιμέρους ανιχνευτών, όσο και του συστήματος σκανδαλισμού, ώστε να αντεπεξέλθει στις νέες υψηλότερων απαιτήσεων συνθήκες. Ο χρόνος απόφασης του L1T θα αυξηθεί από 4 σε 12.5 μs, και ο ρυθμός επιλογής από 100 kHz σε 750 kHz. Όλα τα ηλεκτρονικά του συστήματος σκανδαλισμού θα αντικατασταθούν με νέα, που θα αντικατοπτρίζουν και την αντίστοιχη πρόοδο της τεχνολογίας. Οι σημαντικότερες αναβαθμίσεις περιλαμβάνουν την αντικατάσταση των καλοριμέτρων από νέα, υψηλής διακριτικής ικανότητας, καθώς και την πρόσβαση του συστήματος σκανδαλισμού των μιονίων στα δεδομένα του ανιχνευτή τροχιών (tracker).

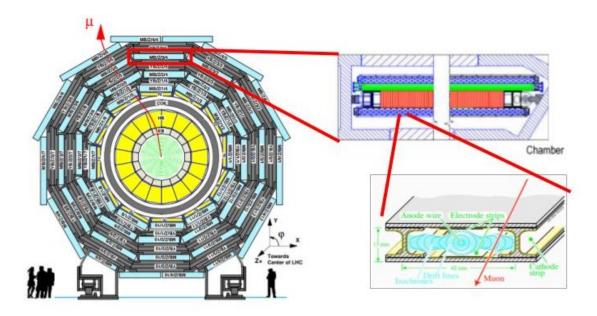

### Το σύστημα σκανδαλισμού μιονίων

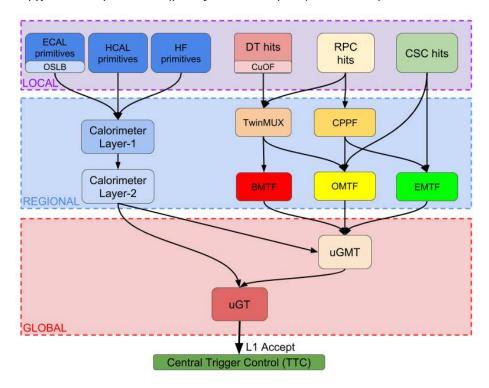

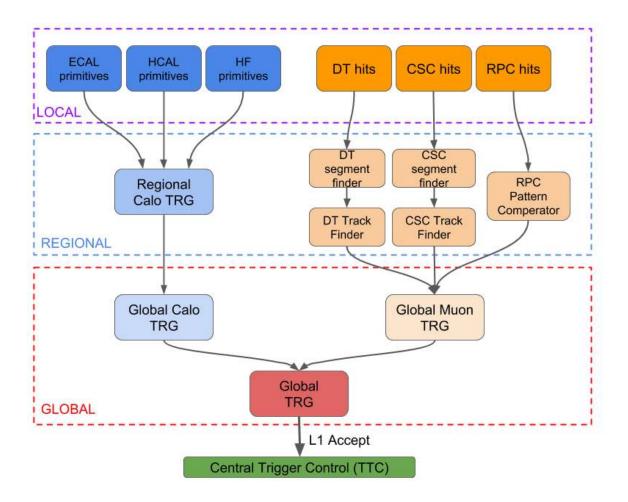

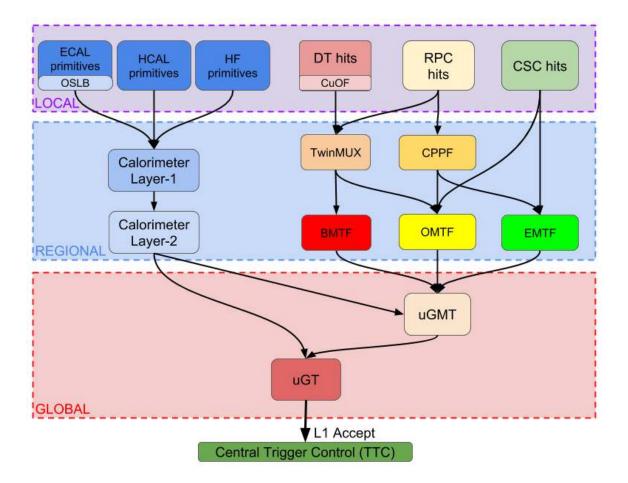

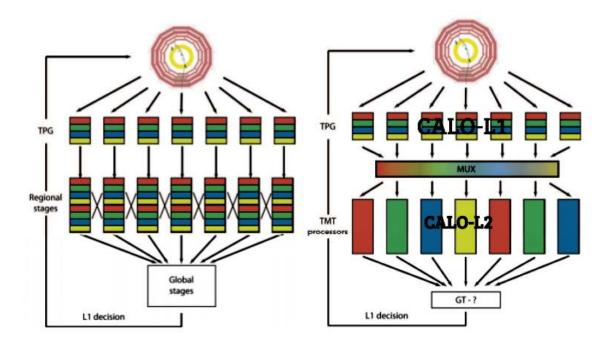

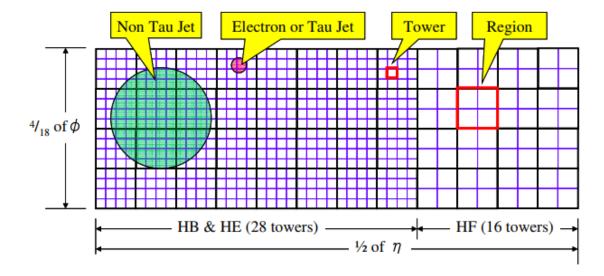

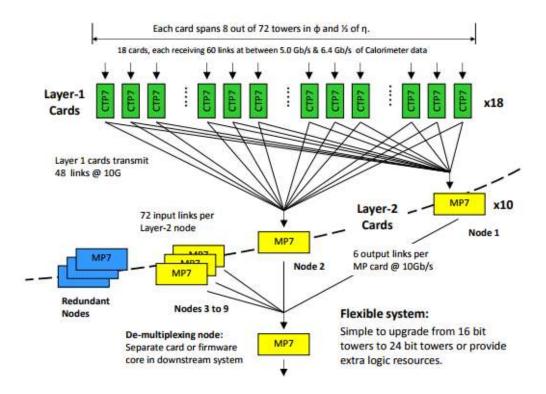

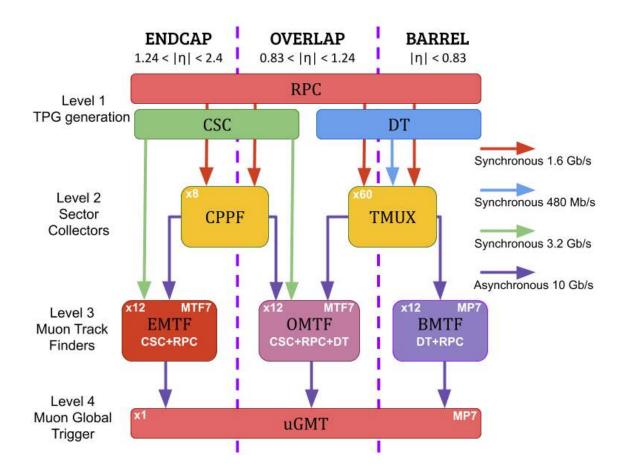

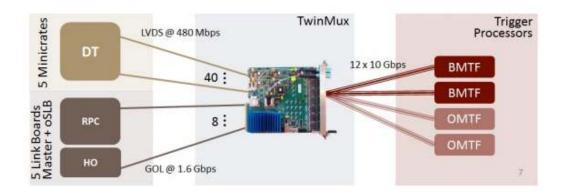

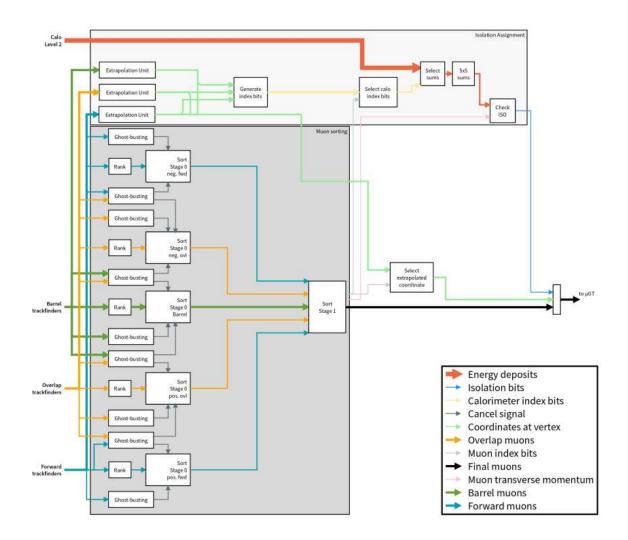

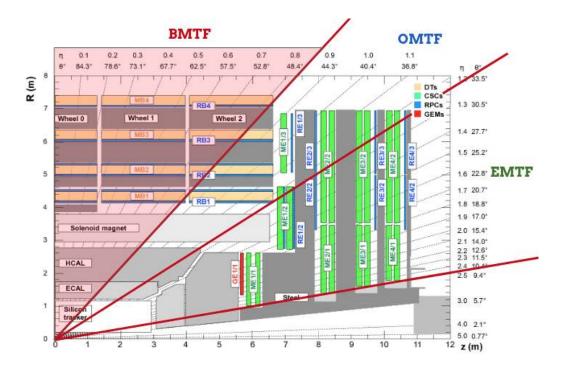

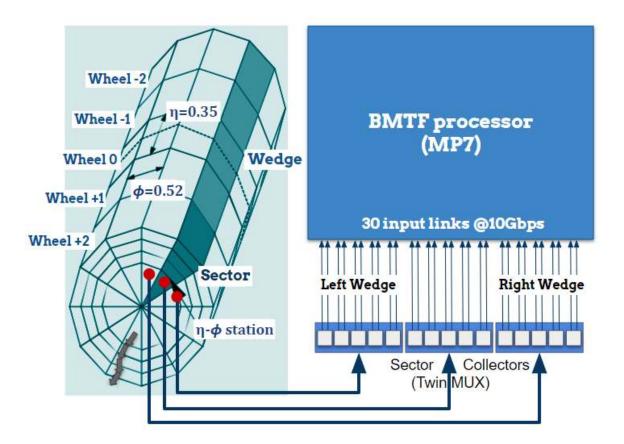

Το πρώτο επίπεδο σκανδαλισμού του CMS χωρίζεται σε δύο ομάδες υποσυστημάτων σκανδαλισμού: τον σκανδαλισμό του καλοριμέτρου (calorimeter trigger) και τον σκανδαλισμό των μιονίων (muon trigger). Το σύστημα σκανδαλισμού μιονίων απαρτίζεται χωρικά από ανιχνευτές τροχιών μιονίων, οι οποίοι λαμβάνουν δεδομένα που παράγονται σε τρεις τύπους ανιχνευτών: τους ανιχνευτές θαλάμων ολίσθησης (Drift Tubes, DT) στην περιοχή του βαρελιού, τους ανιχνευτές θαλάμων καθοδικών λωρίδων (Cathode Strip Chambers, CSC) στην περιοχή των άκρων, και τους θαλάμους επιφανειών υψηλής αντιστάσεως (Resistive Plate Chambers, RPC) που καλύπτουν και τις δύο περιοχές. Στην περιοχή του βαρελιού, το σύστημα σκανδαλισμού αποτελείται από 60 ηλεκτρονικές κάρτες (TwinMUX), που συλλέγουν τα δεδομένα από τους θαλάμους DT και τους θαλάμους RPC, και από 12 ευρετές τροχιών (Barrel Muon Track Finders - BMTF). Η αρχιτεκτονική του συστήματος σκανδαλισμού φαίνεται στην εικόνα 2.

Εικόνα 2: Η αρχιτεκτονική του πρώτου επιπέδου του συστήματος σκανδαλισμού του CMS κατά την διάρκεια του Run 2.

#### Το σύστημα σκανδαλισμού μιονίων στην περιοχή του Βαρελιού

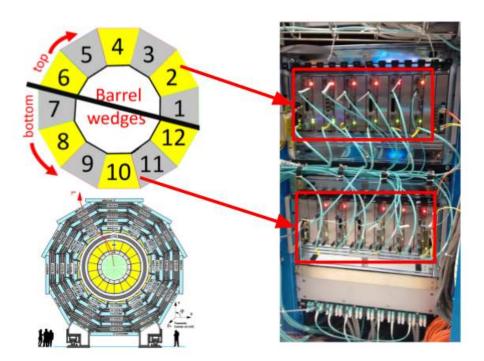

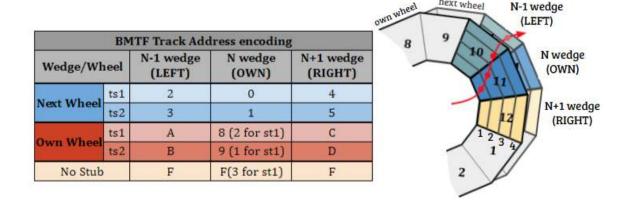

Το σύστημα σκανδαλισμού των μιονίων του CMS στην περιοχή του Βαρελιού, καλύπτει την περιοχή με ψευδοωκύτητα  $0.83 < |\eta|$ . Οι ανιχνευτές DT και RPC ομαδοποιούνται σε 12 τμήματα (wedges) ανοίγματος 30 μοιρών στο  $\phi$ . Κάθε τμήμα χωρίζεται σε 5 τομείς (sectors),

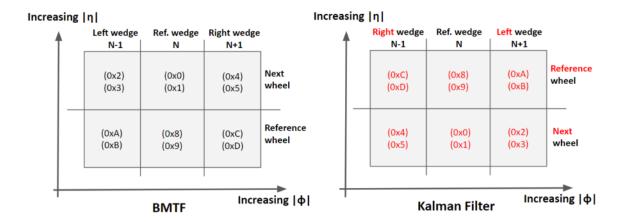

και κάθε sector αποτελείται από 4 DTs και 3 RPCs. Τα αναλογικά σήματα των ανιχνευτών, από κάθε sector, μετατρέπονται σε ψηφιακά και αποστέλλονται σε μια κάρτα πολυπλεξίας και διανομής, την TwinMUX. Οι κάρτες αυτές συνδυάζουν την πληροφορία από τα DTs και τα RPCs, κατασκευάζοντας τα λεγόμενα super-primitives, τα οποία αποστέλλονται στους 12 ευρετές τροχιών μιονίων (BMTF). Κάθε ευρετής τροχιών λαμβάνει πληροφορία από τους 5 sectors, που ανήκουν στο ίδιο Wedge, και από τους 5 sectors των δυο γειτονικών wedges.

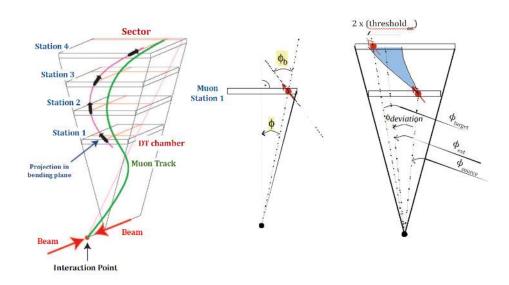

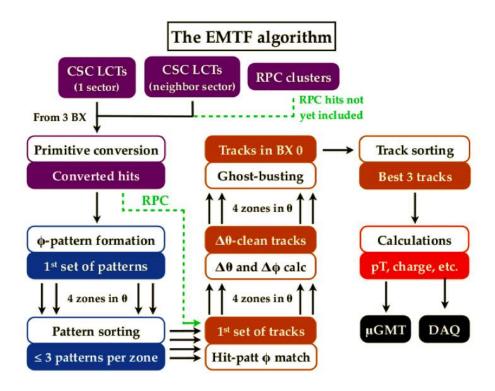

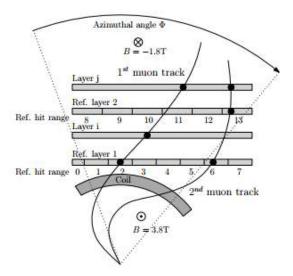

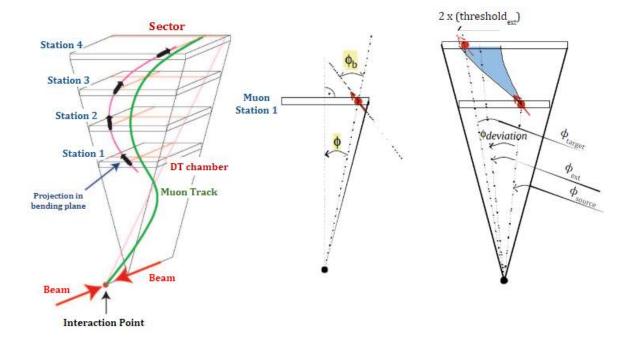

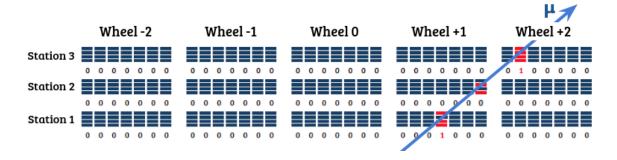

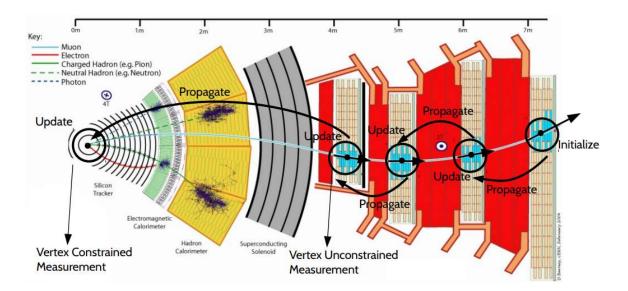

Ο BMTF συνδυάζει τα super-primitives και ανακατασκευάζει τις τροχιές των μιονίων, ξεκινώντας από τα ίχνη που βρίσκονται πλησιέστερα στο σημείο αλληλεπίδρασης. Για τον συνδυασμό των ιχνών, χρησιμοποιεί τις χωρικές συντεταγμένες τους ( $\phi$ -hits,  $\eta$ -hits), τη γωνία διέλευσης του μιονίου ( $\phi_b$ ), και προσπαθεί να τα αντιστοιχίσει με ίχνη σε συγκεκριμένες περιοχές των πιο απομακρυσμένων σταθμών ανίχνευσης. Τα όρια αυτά είναι προϋπολογισμένα και αποθηκευμένα στο FPGA σε πίνακες αντιστοίχησης (LUTs). Η μονάδα συναρμολόγησης της τροχιάς (Track Assembler Unit) συνδυάζει όλα τα πιθανά ζεύγη ιχνών, και συνθέτει μία πλήρη τροχιά. Για την ανακατασκευή μιας τροχιάς, απαιτούνται τουλάχιστον δύο ίχνη. Τέλος, η ηλεκτρονική μονάδα αντιστοίχησης (Assignment Unit), χρησιμοποιώντας επίσης LUTs, αντιστοιχεί σε κάθε τροχιά τις αντίστοιχες φυσικές παραμέτρους (εγκάρσια ορμή  $p_T$ , διεύθυνση  $\phi$  και ψευδοωκύτητα  $\eta$ ) (εικόνα 3).

Εικόνα 3: Ο αλγόριθμος εύρεσης και ανακατασκευής τροχιών μιονίων του συστήματος σκανδαλισμού του CMS, στην περιοχή του βαρελιού, κατά την διάρκεια του Run 2.

Η λογική προ-υπολογισμού και αποθήκευσης των παραμέτρων των μιονίων σε LUTs, καθιστά απαγορευτική τη χρήση περισσότερων από δύο ιχνών για τον υπολογισμό του  $p_T$ , καθώς ο αριθμός συνδυασμών ξεπερνά τις δυνατότητες αποθήκευσης του FPGA. Για την αύξηση της ακρίβειας της μέτρησης του  $p_T$ , ο αλγόριθμος υποθέτει ότι τα μιόνια προέρχονται από το σημείο αλληλεπίδρασης, προσθέτοντας ένα τρίτο σημείο στην τροχιά του. Με αυτή τη μέθοδο βελτιώνει την ποιότητα μέτρησης του  $p_T$ , αλλά καθιστά απαγορευτική την ανακατασκευή τροχιών "μετατοπισμένων" μιονίων. Τα μετατοπισμένα μιόνια είναι δυνατόν να προέλθουν

από μακρόβια, ουδέτερα σωματίδια, τα οποία μπορούν να διασπαστούν μακριά από το αρχικό σημείο αλληλεπίδρασης των πρωτονίων. Για παράδειγμα θα μπορούσαν να προέλθουν από τη διάσπαση υπερσυμμετρικών σωματίων, όπως το προβλεπόμενο Higgsino.

#### Ο νέος αλγόριθμος σκανδαλισμού μιονίων με χρήση ενός φίλτρου Kalman

Ένας νέος αλγόριθμος, με χρήση φίλτρου Kalman, προτάθηκε στις αρχές του 2018 για να επιλύσει το πρόβλημα ανίχνευσης μετατοπισμένων μιονίων. Το φίλτρο Kalman είναι ένας αλγόριθμος που εφαρμόζεται σε συστήματα που δέχονται εξωτερικές φυσικές διαταραχές (θορύβους), με σκοπό τον "καθαρισμό" των μετρήσεων, και τη δημιουργία μιας νέας εκτίμησης της κατάστασης του συστήματος, απογυμνωμένη από διαταραχές.

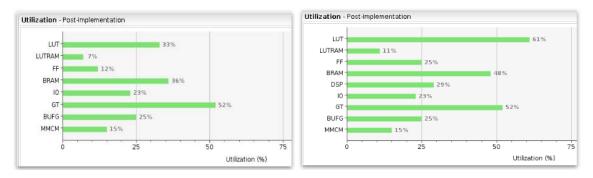

Ξεκινώντας από τον εξωτερικό σταθμό ανίχνευσης μιονίων, οι παράμετροι της τροχιάς  $(p_T,quality,\phi,\phi_b)$  δίνονται από ένα διάνυσμα κατάστασης  $\chi_n$ . Ο αλγόριθμος χρησιμοποιεί έναν πίνακα μετάβασης κατάστασης F, που εξαρτάται από τη γεωμετρία του ανιχνευτή και το μαγνητικό πεδίο B, ώστε να προβλέψει τη θέση στον επόμενο σταθμό ανίχνευσης. Αφού υπολογιστεί η επόμενη κατάσταση, χρησιμοποιούνται οι παράμετροι της πλησιέστερης μέτρησης, που δίνονται με την μορφή ενός διανύσματος μετρήσεων  $z_n$ , και οι παράμετροι του διανύσματος κατάστασης ενημερώνονται. Η διαδικασία επαναλαμβάνεται, μέχρι τον τελευταίο (εσώτερο) σταθμό ανίχνευσης. Σε αυτό το στάδιο, η μέτρηση της εγκάρσιας ορμής  $(p_T)$  του μιονίου αποθηκεύεται, χωρίς την απαίτηση προέλευσης του μιονίου από το σημείο αλληλεπίδρασης, επιτρέποντας και μετατοπισμένα μιόνια. Στη συνέχεια, μια δεύτερη τιμή της  $p_T$  υπολογίζεται, αυτή τη φορά με τον περιορισμό διέλευσης της τροχιάς από το σημείο αλληλεπίδρασης, παρομοίως με τον παλιό αλγόριθμο.

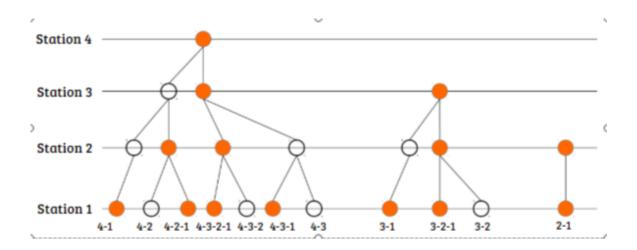

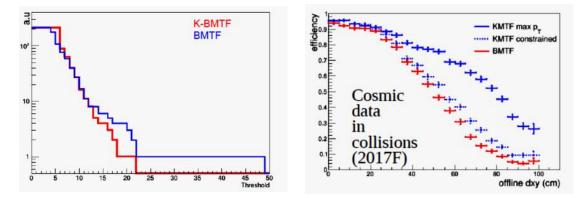

Ο νέος αλγόριθμος σχεδιάστηκε αρχικά για το Phase-2, αλλά ενσωματώθηκε στο σύστημα σκανδαλισμού του Phase-1, παράλληλα με τον παλιό αλγόριθμο. Αυτό κατέστη εφικτό λόγω της εκτεταμένης χρήσης DSPs (σε αντίθεση με τον παλιό αλγόριθμο), της ευελιξίας στο συνολικό διαθέσιμο latency του BMTF, και της περιορισμένης χρήσης πόρων του FPGA από τον παλιό αλγόριθμο. Ο αλγόριθμος Kalman αναπτύχθηκε σε γλώσσα C++, και στην συνέχεια μεταγλωττίστηκε σε VHDL, με τη χρήση του λογισμικού Vivado High Level Synthesis της Xilinx. Για την ενσωμάτωση του νέου αλγορίθμου, αναπτύχθηκε κώδικας που υλοποιεί την διεπαφή του με το firmware της BMTF. Οι παράμετροι εισόδου τροποποιήθηκαν κατάλληλα, λαμβάνοντας υπόψιν τις ιδιαιτερότητες του νέου αλγορίθμου. Επιπλέον, πραγματοποιήθηκε βελτιστοποίηση του firmware, με την προσθήκη επιπλέον καταχωρητών και επιλογή ειδικών στρατηγικών, ώστε όλα τα στοιχεία του νέου αλγόριθμου να είναι συγχρονισμένα. Η ορθή λειτουργία του νέου firmware, ελέγχθηκε εκτεταμένα στο εργαστήριο, με την ανάπτυξη λογισμικού και firmware (test benches). Τέλος το νέο firmware ελέγχθηκε με πραγματικά δεδομένα στο CMS.

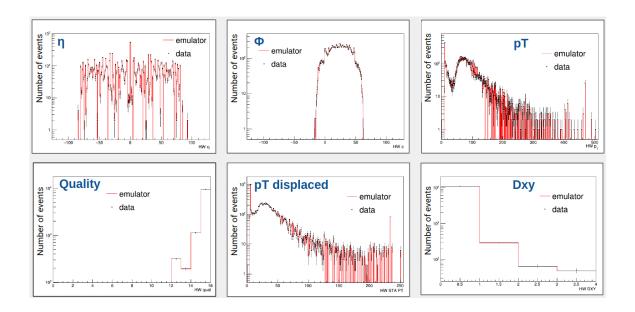

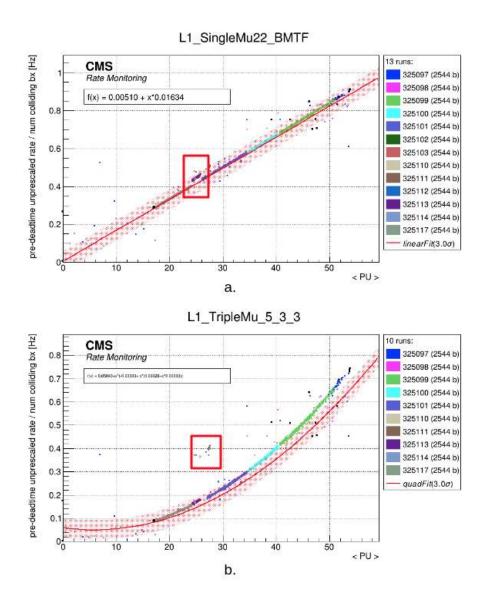

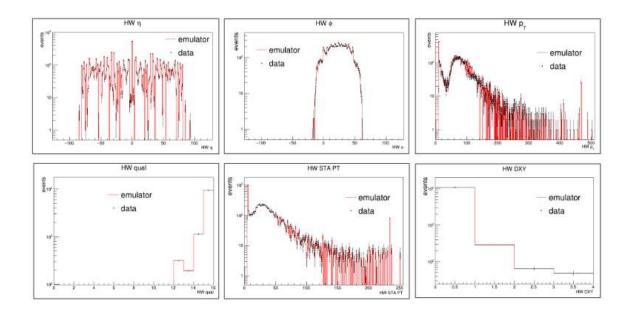

Στην εικόνα 4 μπορούμε να δούμε μια σύγκριση των παραμέτρων των μιονίων, μεταξύ των πραγματικών δεδομένων με αυτά του εξομοιωτή (emulator). Παρατηρείται πολύ καλή συμφωνία, της τάξης του 99.6%. Το όριο για να γίνει αποδεκτός ένας νέος αλγόριθμος από το CMS είναι 99%, το οποίο και επιτεύχθηκε.

Εικόνα 4: Σύγκριση των παραμέτρων των μιονίων, μεταξύ των πραγματικών δεδομένων με αυτά του εξομοιωτή (emulator).

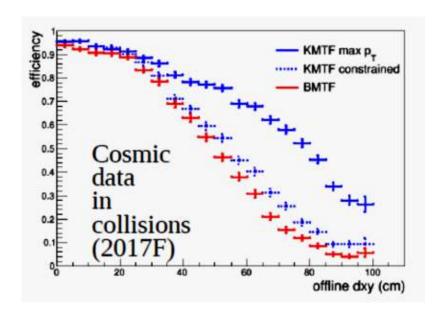

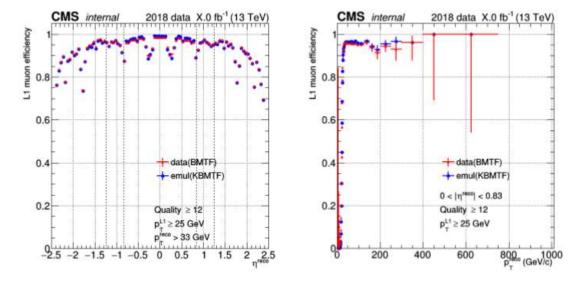

Στην εικόνα 5, φαίνεται η απόδοση ανίχνευσης μετατοπισμένων μιονίων με τη χρήση του παλιού αλγορίθμου (με κόκκινο) και με τη χρήση του νέου αλγορίθμου, με τον περιορισμό του σημείου αλληλεπίδρασης (με γαλάζιο) και χωρίς (με μπλε). Είναι εμφανής η βελτίωση για μιόνια με προέλευση από 20 έως 100 cm μακριά από το σημείο αλληλεπίδρασης.

#### Η δοκιμαστική ηλεκτρονική κάρτα L1-BMT

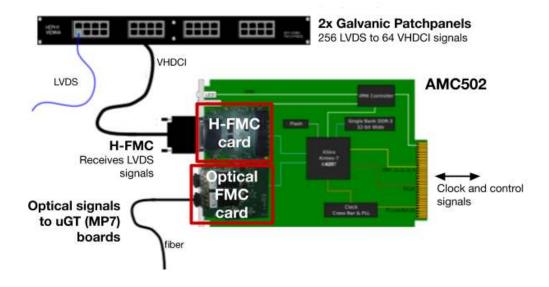

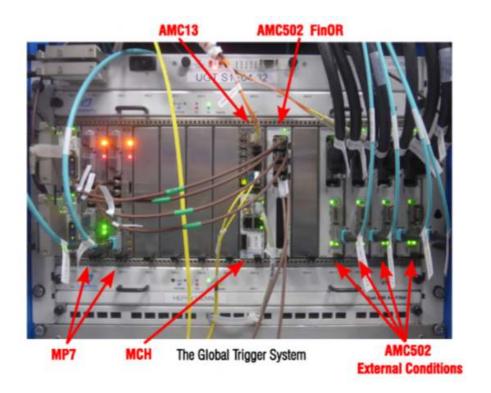

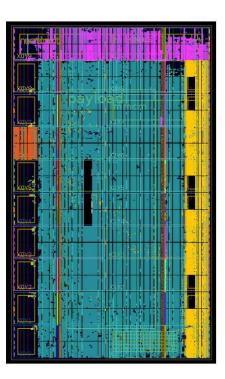

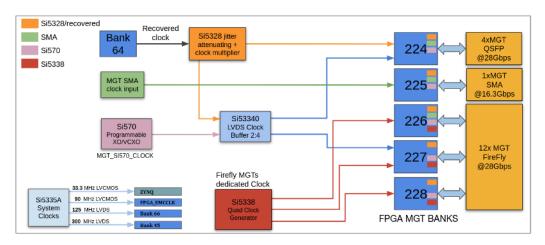

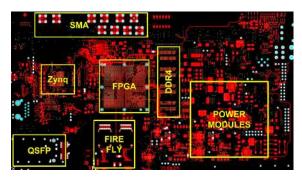

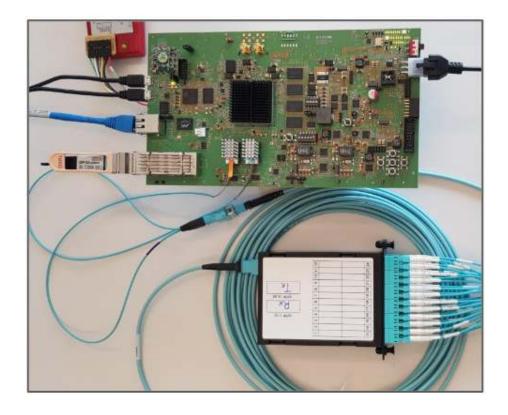

Στο πλαίσιο της έρευνας και ανάπτυξης νέου υλισμικού για την περίοδο Phase-2 του LHC, σχεδιάστηκε και κατασκευάστηκε μια νέα αναπτυξιακή ηλεκτρονική κάρτα, η L1-BMT, για το σύστημα σκανδαλισμού του CMS στην περιοχή του βαρελιού (εικόνα 6). Η κάρτα αυτή, παρέχει ένα περιβάλλον για την ανάπτυξη και την αξιολόγηση νέων αλγορίθμων και τεχνολογιών. Στην καρδιά της κάρτας βρίσκεται το XCKU040, ένα Kintex Ultrascale FPGA τελευταίας γενιάς από την Xilinx, που παρέχει, μεταξύ άλλων, 20 Multi-Gigabit transceivers (MGT) με μέγιστη ταχύτητα 16 Gbps. Δώδεκα MGTs είναι συνδεδεμένοι με τα οπτικά στοιχεία Fireflys, της Samtec, υπεύθυνες για τη μετατροπή του ηλεκτρικού σήματος σε οπτικό. Επιπλέον, τέσσερις MGTs συνδέθηκαν με ένα QSFP. Τα Fireflys έχουν επιλεγεί από το πείραμα CMS για να χρησιμοποιηθούν στις ηλεκτρονικές κάρτες του συστήματος σκανδαλισμού του Phase-2. Η κάρτα, επίσης, παρέχει δύο προγραμματιζόμενες γεννήτριες συχνοτήτων υψηλής ακρίβειας, και έναν διαφορικό SMA connector, για το χρονισμό της λογικής και των transceivers του FPGA. Επιπλέον, όλα τα προγραμματιζόμενα στοιχεία της κάρτας (π.χ γεννήτριες συχνοτήτων, Fireflys, QSFP κτλ) ελέγχονται από ένα System-on-Chip FPGA (Zynq XC7Z010). Τέλος, το Kintex FPGA και το Zynq μπορούν να προγραμματιστούν μέσω JTAG.

Εικόνα 5: Απόδοση ανίχνευσης μετατοπισμένων μιονίων του παλιού αλγορίθμου (με κόκκινο), και του νέου αλγορίθμου με τον περιορισμό της διέλευσης από το σημείο αλληλεπίδρασης (με γαλάζιο) και χωρίς (με μπλέ).

Εικόνα 6: Η αναπτυξιακή ηλεκτρονική κάρτα L1-BMT, για το σύστημα σκανδαλισμού του CMS στην περιοχή του βαρελιού.

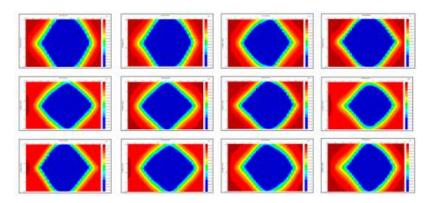

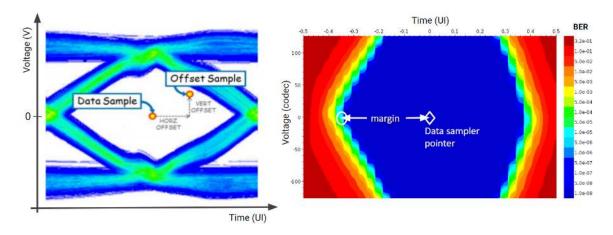

Η λειτουργία των οπτικών links της κάρτας ελέγχθηκε χρησιμοποιώντας το ενσωματωμένο Bit Error Rate Test (iBERT) της Xilinx. Το iBERT μας δίνει τη δυνατότητα υπολογισμού του ρυθμού εισαγωγής σφαλμάτων κατά τη μετάδοση δεδομένων, καθώς και την ανοχή του καναλιού σε θόρυβο, με τη χρήση των λεγόμενων eyescans. Τα eyescans είναι δισδιάστατα ιστογράμματα τα οποία κατασκευάζονται προσθέτοντας ένα offset στον χρόνο (οριζόντιος άξονας) και στην

τάση (κατακόρυφος άξονας) της λαμβανόμενης ψηφιακής πληροφορίας, και μετρώντας κάθε φορά το BER.

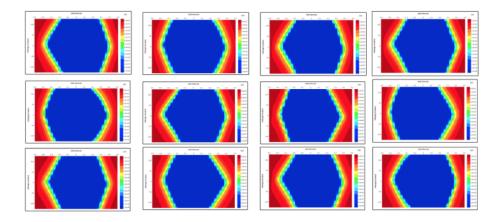

Στην εικόνα 7, φαίνονται τα eyescans για τα 12 Firefly links στα 16 Gbps. Παρατηρούμε ότι η μπλε περιοχή, που αντιστοιχεί σε μηδενικό BER, είναι ευρεία και βρίσκεται στο κέντρο του διαγράμματος, πράγμα που υποδεικνύει πολύ καλή ποιότητα καναλιού με ανοχή στον θόρυβο.

Εικόνα 7: Eyescans για τα 12 Firefly links στα 16 Gbps.

### Το πρωτόκολλο επικοινωνίας "Hermes".

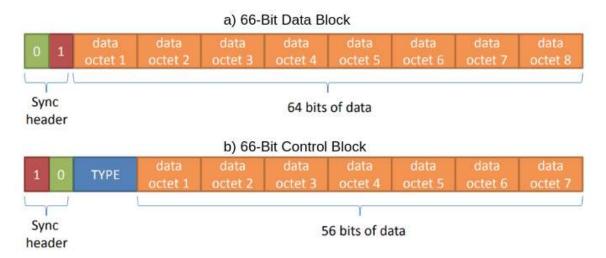

Ακολουθώντας τα υπόλοιπα υποσυστήματα του πειράματος, το πρωτόκολλο επικοινωνίας των links του συστήματος σκανδαλισμού του CMS θα πρέπει να αναβαθμιστεί, ώστε να αντεπεξέλθει στις νέες απαιτητικές συνθήκες που θα προκύψουν μετά την αναβάθμιση του LHC. Στο πλαίσιο της αναβάθμισης αυτής, σχεδιάστηκε το πρωτόκολλο επικοινωνίας "Hermes", βασιζόμενο στα τελευταίας γενιάς Ultrascale και Ultrascale+ FPGAs, με ενσωματωμένους transceivers GTH/GTY, που φτάνουν σε ταχύτητες 32 Gbps. Το νέο πρωτόκολλο ενσωματώνει την κωδικοποίηση 64b66b, η οποία προσθέτει μόνο 3.125% επιπλέον πληροφορίας (overhead), έναντι 20% της παλιάς κωδικοποίησης 8b10b. Για να καλύψει τις ανάγκες του νέου συστήματος σκανδαλισμού, το πρωτόκολλο θα πρέπει να έχει τα εξής βασικά χαρακτηριστικά:

- 1. Χαμηλό latency, λόγω του περιορισμένου συνολικού διαθέσιμου latency του συστήματος σκανδαλισμού.

- 2. Περιορισμένη χρήση πόρων στο FPGA, που θα αφήνει περισσότερο χώρο για τη λογική των αλγορίθμων.

- 3. Ασύγχρονη λειτουργία με το ρολόι του LHC, το οποίο παρουσιάζει διακυμάνσεις στη φάση του, ικανές να απο-συγχρονίσουν τους transceivers.

- 4. Συγχρονισμός και αυτόματη ανάκτηση της σύνδεσης, ώστε να εξοικονομηθεί πολύτιμος χρόνος, σε περίπτωση προσωρινής διακοπής στην αποστολή δεδομένων.

5. Ανίχνευση σφαλμάτων, η οποία θα επιτρέπει τον έλεγχο της ορθότητας των δεδομένων.

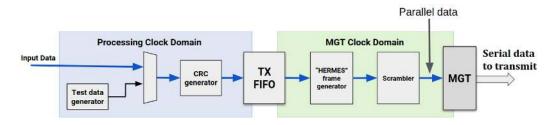

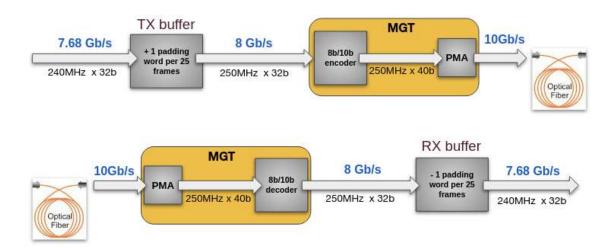

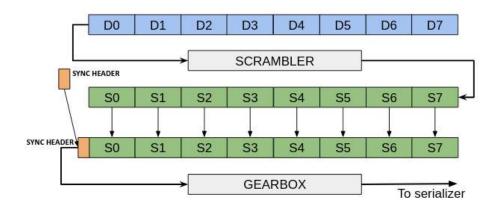

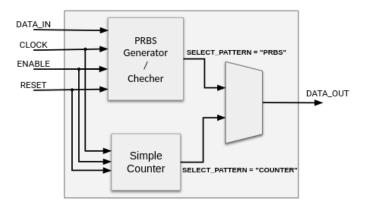

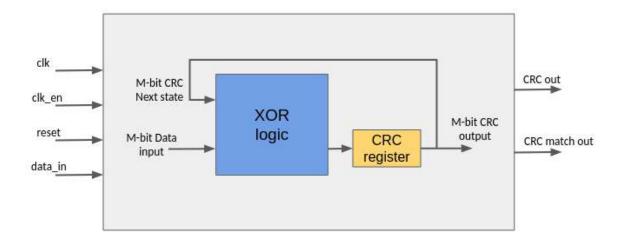

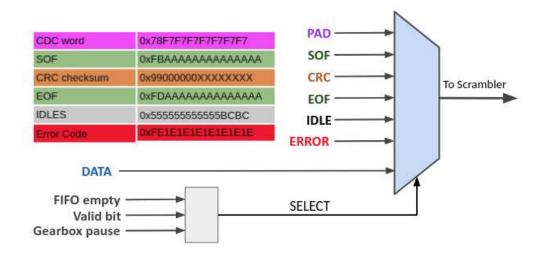

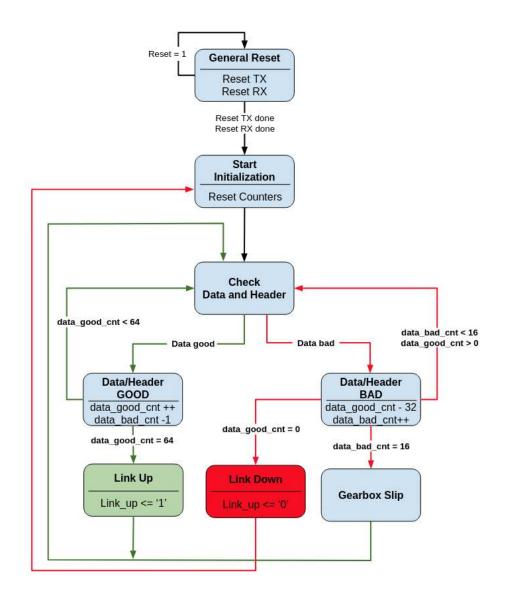

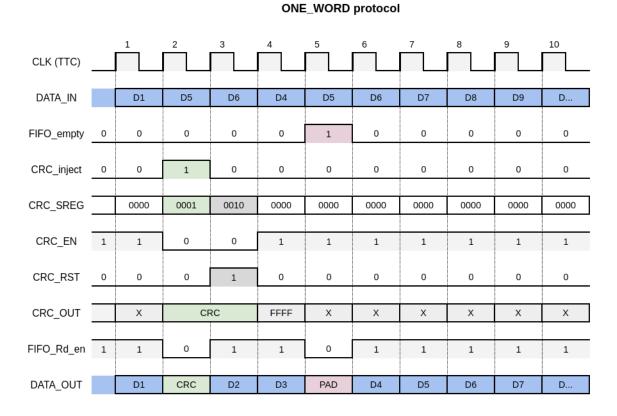

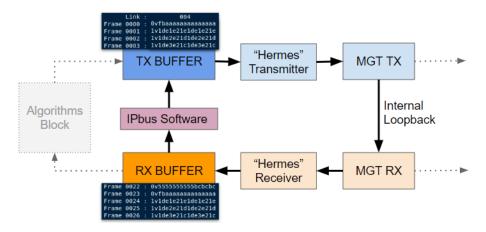

Στην εικόνα 8, φαίνεται ένα απλοποιημένο σχηματικό διάγραμμα του πομπού. Σε κανονική λειτουργία, τα δεδομένα προς μετάδοση προέρχονται από τους αλγόριθμους. Σε λειτουργία ελέγχου, μπορούμε να επιλέξουμε να στείλουμε δεδομένα από μια γεννήτρια ψευδοτυχαίων αριθμών ή από έναν μετρητή 16-bit. Τα δεδομένα εισέρχονται στη γεννήτρια CRC, η οποία παράγει ένα checksum, που αποστέλλεται μετά το τέλος της ροής δεδομένων. Στη συνέχεια, τα δεδομένα, μέσω μιας μνήμης FIFO, περνούν από το ρολόι του LHC στο πιο σταθερό, και ελαφρώς πιο γρήγορο, ρολόι του transceiver. Όταν η μνήμη αδειάσει, διακόπτουμε προσωρινά την ανάγνωση, εισάγοντας ψευδο-δεδομένα (filler blocks). Στη συνέχεια, τα δεδομένα κωδικοποιούνται σύμφωνα με το πρωτόκολλο "Hermes". Κωδικοποιημένες λέξεις προστίθενται για να δηλώσουν την αρχή (Start of Frame - SoF) και το τέλος (End of Frame - EoF) της ροής δεδομένων, ενώ όλα τα δεδομένα που δεν θα χρησιμοποιηθούν από τους αλγόριθμους, αντικαθίστανται από κωδικοποιημένες λέξεις (IDLEs). Στη συνέχεια, τα δεδομένα εισέρχονται σε έναν περιπλέκτη (scrambler), ο οποίος τυχαιοποιεί την αλληλουχία των bits, δίνοντάς τους τα κατάλληλα ηλεκτρικά χαρακτηριστικά. Τέλος, τα δεδομένα εισέρχονται στον transceiver, ο οποίος τα διαμορφώνει κατάλληλα, τα μετατρέπει σε παράλληλα, και τα αποστέλλει.

Εικόνα 8: Απλοποιημένο σχηματικό διάγραμμα του πομπού.

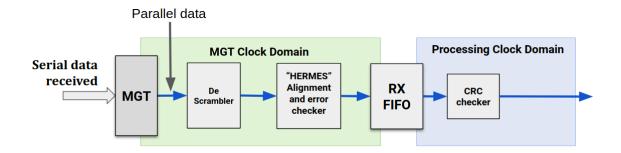

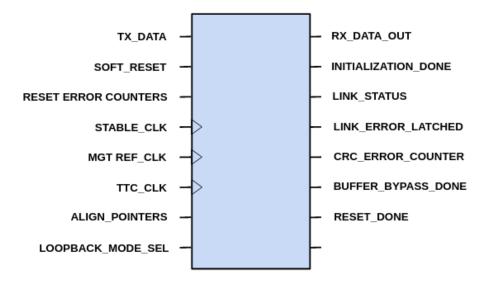

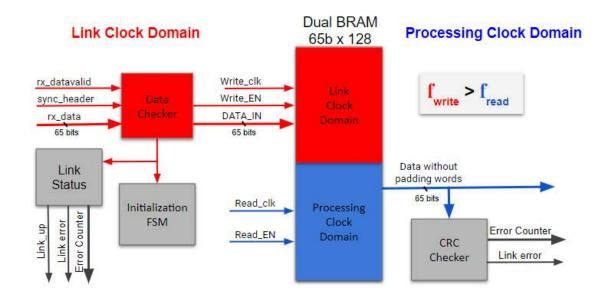

Στην εικόνα 9, φαίνεται ένα απλοποιημένο σχηματικό διάγραμμα του δέκτη. Τα δεδομένα λαμβάνονται από τον δέκτη του transceiver, μετατρέπονται σε παράλληλα, και στέλνονται στον απο-περιπλέκτη (de-scrambler). Στη συνέχεια, οι κωδικοποιημένες λέξεις του πρωτοκόλλου και ο 2-bit header της 64b66b κωδικοποίησης, ελέγχονται για σφάλματα. Στο στάδιο αυτό, πραγματοποιείται και η ευθυγράμμιση του link. Για κάθε 16 συνεχόμενα σφάλματα, ο δείκτης που καθορίζει το πρώτο bit των παράλληλων λέξεων στον transceiver, μετακινείται κατά μια θέση. Με την ορθή λήψη των δεδομένων, η ευθυγράμμιση έχει ολοκληρωθεί. Η διαδικασία επαναλαμβάνεται αυτόματα, σε περίπτωση λήψεως μεγάλου αριθμού σφαλμάτων, που υποδεικνύουν απώλεια του συγχρονισμού. Μετά τον έλεγχο, τα filler blocks αφαιρούνται, και με την χρήση μίας μνήμης BRAM μεταβαίνουν από το ρολόι του transceiver στο ρολόι του LHC. Τέλος, μια γεννήτρια CRC αναπαράγει το checksum, χρησιμοποιώντας την λαμβανόμενη ροή δεδομένων, και το συγκρίνει με το αντίστοιχο checksum που υπολογίστηκε στον πομπό. Σε περίπτωση διαφωνίας, αυξάνει κατά μία μονάδα ένας καταχωρητής καταμέτρησης σφαλμάτων.

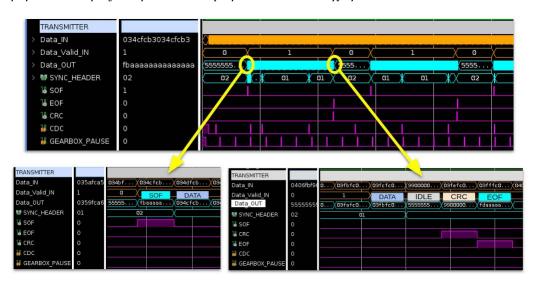

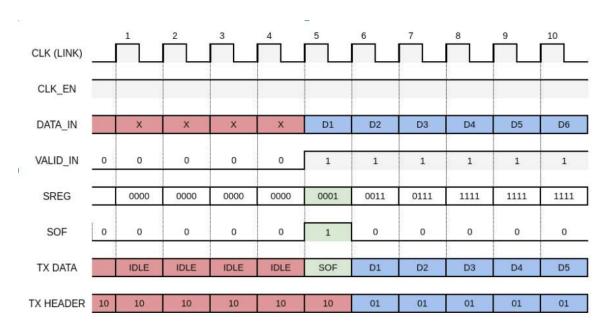

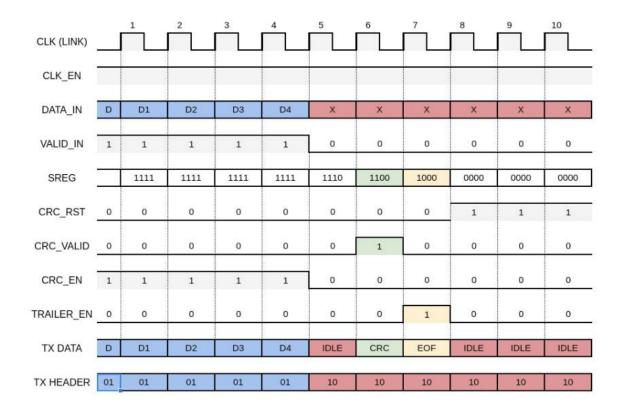

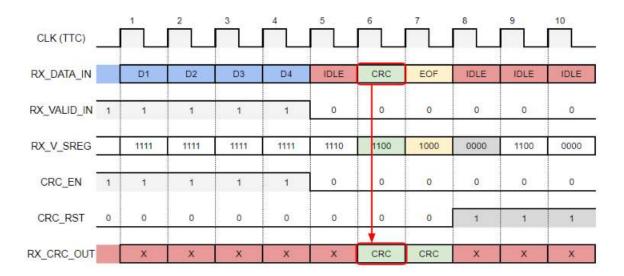

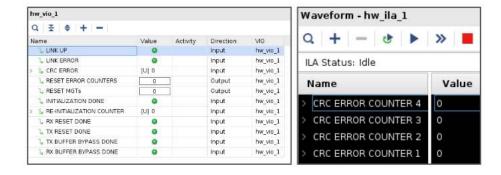

Ο έλεγχος ορθής λειτουργίας του κωδικοποιητή πραγματοποιήθηκε με προσομοίωση του firmware, χρησιμοποιώντας το λογισμικό *Vivado* της Xilinx. Στην εικόνα 10, παρουσιάζεται η διαμόρφωση των δεδομένων, με την προσθήκη των κωδικοποιημένων λέξεων στην αρχή (SoF) και

Εικόνα 9: Απλοποιημένο σχηματικό διάγραμμα του δέκτη.

στο τέλος (CRC, EoF) της ροής δεδομένων. Ο έλεγχος της κωδικοποίησης πραγματοποιήθηκε και σε επίπεδο hardware, αποθηκεύοντας τα λαμβανόμενα δεδομένα σε μια προσωρινή μνήμη στον δέκτη, η οποία διαβάζεται με ειδικό λογισμικό που αναπτύχθηκε.

**Εικόνα 10**: Προσομοίωση του κωδικοποιητή. Προσθήκη των κωδικοποιημένων λέξεων SoF (κάτω αριστερά) και CRC, ΕοF (κατω δεξιά).

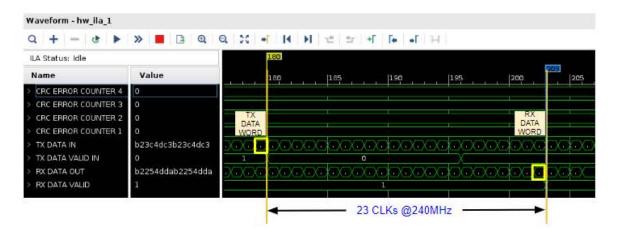

Για τη μέτρηση του latency των links, χρησιμοποιήθηκε ο ενσωματωμένος λογικός αναλυτής της Xilinx, και ελήφθησαν μετρήσεις, για ταχύτητες 16 Gbps και 25 Gbps. Η μέθοδος που χρησιμοποιήθηκε ήταν η αποστολή μιας δοκιμαστικής λέξης, και η μέτρηση των κύκλων ρολογιού μέχρι αυτή να εμφανιστεί στον πομπό. Στα 16 Gbps, με συχνότητα του παράλληλου ρολογιού ίση με 240 MHz, μετρήθηκαν 23 κύκλοι (ή ισοδύναμα 3.8 BXs¹). Αντίστοιχα, στα 25 Gbps, με συχνότητα του παράλληλου ρολογιού ίση με 360 MHz, μετρήθηκαν 27 κύκλοι (ή ισοδύναμα 3 BXs).

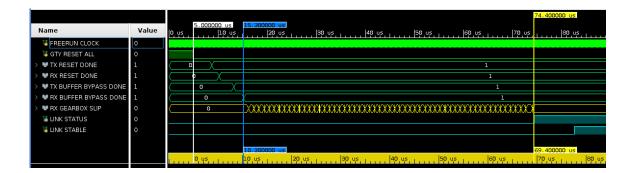

Τέλος, για την αξιολόγηση της σταθερότητα των links στα 16 Gbps, χρησιμοποιήθηκαν

24

<sup>&</sup>lt;sup>1</sup>Ένα BX ή Bunch Crossing, είναι ίσο με την περίοδο του LHC clock, δηλαδή 25 ns.

διάφορες αναπτυξιακές κάρτες (ΚCU105, L1-BMT), στέλνοντας δεδομένα σε εσωτερικό loopback, αλλά και μέσω οπτικής ίνας μήκους 20 m. Και στις δύο περιπτώσεις, στάλθηκαν δεδομένα επί 72 ώρες, χωρίς να παρουσιαστεί σφάλμα. Αυτό μεταφράζεται σε  $BER < 2.41 \times 10^{-16}$ . Για τον έλεγχο των links στα 25 Gbps, χρησιμοποιήθηκε η κάρτα Serenity, η οποία σχεδιάστηκε και κατασκευάστηκε από το Imperial College για το Phase-2. Επίσης στάλθηκαν δεδομένα για 72 ώρες, χωρίς να παρουσιαστεί σφάλμα, γεγονός που μεταφράζεται σε  $BER < 1.54 \times 10^{-16}$ .

## Chapter 1

### Introduction

The Large Hadron Collider (LHC) is the world's largest and most powerful particle accelerator at the CERN research laboratory. It consists of a 27-kilometre ring of superconducting magnets, with a number of accelerating structures to boost the energy of the particles. LHC's main purpose is to accelerate protons or ions in the form of two high-energy beams travelling in opposite directions at a speed close to the speed of light. The beams collide at four points, where the two rings of the machine intersect and at each point a detector was built around the collision point.

The Compact Muon Solenoid (CMS) detector is one of the two large multi-purpose detectors operating at the LHC. Its physics program ranges from studying the Standard Model, including the Higgs boson, to searching for extra dimensions and particles that could make up dark matter. Great emphasis, however, has been given to the discovery of the predicted Higgs boson, due to its key role in understanding the nature of the electroweak symmetry breaking. The experimental study of the Higgs mechanism, can also shed light on the mathematical consistency of the Standard Model at energy scales above about 1 TeV.

During Phase-1 of the LHC program (2011-2023) the instantaneous luminosity reached  $2\times 10^{34}~cm^{-1}s^{-1}$ , with a pile-up of about 50. This number of events produces an enormous amount of raw data that exceeds 40 Petabytes per second. In order to deal with that amount of data, a sophisticated electronics system was built, responsible of reducing this rate by at least a factor of  $10^6$ , through a physics event selection process. The rate reduction is performed in two steps; the Level-1 Trigger (L1T) and the High Level Trigger (HLT). The L1T is a high-bandwidth, fixed latency system based on Field-Programmable Gate Arrays (FPGAs) that receives data from the calorimeters and the muon system and reduces the rate to 100 kHz.

After the end of Run 3 (2023) the LHC will undergo a major upgrade. The new configuration, known as High Luminosity LHC (HL-LHC), will rely on a number of key innovations that push accelerator technology beyond its present limits. The main target of the HL-LHC is to increase the peak instantaneous luminosity to  $5 \times 10^{34} \ cm^{-2} s^{-1}$ . This will allow an integrated luminosity

of 250  $fb^{-1}$  per year, with the goal of 3000  $fb^{-1}$  in over 10 to 12 years after the upgrade. The CMS collaboration will have to upgrade the experiment, in order to cope effectively with the higher pile up and maintain data quality, by limiting the degradation due to aging and radiation damage. Furthermore, the trigger system must increase its selectivity and the capacity of the readout system. CMS has decided to increase the L1T latency to 12.5  $\mu s$  from 4  $\mu s$  for the legacy system, while the read out data rate at a higher rate limit will increase to 750 kHz compared to 100 kHz of the legacy trigger.

In chapter 2, a short description of the LHC is given, followed by the presentation of the CMS detector and its subsystems in chapter 3. A small summary of the technologies being used by the various electronics systems of the CMS trigger follows in chapter 4 and a detailed presentation of the L1T system is presented in chapter 5.

#### Contributions and thesis overview

The main contribution of this dissertation was the improvement of the Level-1 Trigger Muon Track Finder algorithms in the Central Region of the CMS detector, as well as related R&D projects for the HL-LHC.

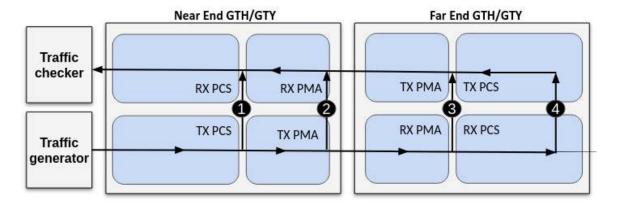

Firstly, a low latency asynchronous protocol for high speed links was designed, implemented and tested. The protocol was designed to meet the needs of the Phase-2 CMS trigger systems and will run at rates of 16 - 28 Gbps, improving the performance of the current 10 Gbps links up to 400%. The firmware was tested in various CMS Phase-2 board demonstrators (*Serenity* [1], *L1-BMT*, *Ocean* [2]), using Xilinx Ultrascale and Ultrascale+ FPGAs. An extensive description of the firmware, the link functionality and the test results are presented in chapter 7.

At the end of 2017, an upgrade of the Level 1 muon tracking algorithm was presented by the CMS UCLA group, featuring an FPGA embedded Kalman Filter, implemented using High Level Synthesis (HLS) [3] tools. The possibility of testing the algorithm was investigated with real data during Run 2 (2017 - 2018). The firmware was integrated in the CMS data taking, running in parallel with the current algorithm, by implementing both algorithms into the same FPGA. This required tackling many challenges like latency optimization, area optimization, meeting timing constraints and running an HLS algorithm in parallel with the old algorithm written in VHDL. The new algorithm will be the default standalone algorithm for Run 3 (2021-2023). This is considered a breakthrough, since it was the he first time an HLS based algorithm was used at a CMS trigger subsystem. The new algorithm is optimised to identify displaced muons, creating new opportunities for the physics groups searching for long-lived particles. An overview of the algorithm and the integration, testing and commissioning of the new firmware is presented in chapter 6.

Finally, within the scope of Phase-2 R&D, a new L1T processor card was designed by the Greek CMS Trigger team, to provide a hardware environment for developing and evaluating the new L1T muon algorithms and links. The board comes with state-of-the-art fiber optics

technologies, using micro footprint optical interconnects. An overview of the board along with the testing and debugging of the high-speed optical links and the integration of the Hermes link protocol is presented in chapter 6.

29

## **Chapter 2**

# The Large Hadron Collider

The Large Hadron Collider is the world's largest and most powerful particle accelerator and its main purpose is to accelerate protons or ions. It consists of a 27-kilometre ring of superconducting magnets, with a number of accelerating structures to boost the energy of the particles. The particles form two high-energy beams travelling in opposite directions at a speed close to the speed of light. They collide at four points where the two rings of the machine intersect. Thousands of magnets of different varieties and sizes are used to direct the beams around the accelerator. These include 1232 dipole magnets, 15 metres in length, that bend the beams, and 392 quadrupole magnets, each 5–7 metres long, which focus the beams. Just prior to collision, another type of magnet is used to "squeeze" the particles closer together to increase the chances of collisions. The particles are so tiny that the task of making them collide is akin to firing two needles 10 kilometres apart with such precision that they meet halfway.

The electromagnets are built from coils of special electric cable that operates in a superconducting state, efficiently conducting electricity without resistance or loss of energy. This requires chilling the magnets to -271.3°C - a temperature colder than outer space. For this reason, much of the accelerator is connected to a distribution system of liquid helium, which cools the magnets, as well as to other supply services. The LHC structure is housed 100 metres underground, in a circular tunnel once in use by another machine, Large Electron-Positron Collider (LEP), that was dismantled in 2000. Hadrons are injected into the LHC from a chain of smaller accelerators that drives them up to higher energies.

### 2.1 The LHC injector chain

Protons are created in an ion source called *duoplasmatron*, from which they are extracted with an energy of 50 KeV. They are then injected to LINAC2, a 35 meter long Linear Accelerator and their energy is increased to 50 MeV. The beam is further increased to 1.4 GeV, in the Proton Synchrotron

Booster (PSB), before they continue their journey to the Proton Synchrotron (PS). Here the particles are grouped into a train of bunches of  $10^11$  protons, 1.2 m long and 7 m apart. Their energy increases to 26 GeV.

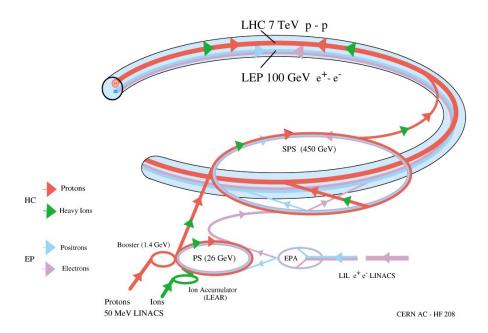

Figure 2.1: Illustration of the CERN accelerator complex. The LHC is supplied with protons or heavy ions by the SPS via two transfer lines, which additionally provide beams to several non-LHC experiments. The SPS is fed with pre-accelerated protons by the PS, CERN's first synchrotron. The first circular accelerator in the proton-proton injection chain is PSB which is filled by the linear accelerator LINAC2. For beams of heavy ions the injection chain begins with LINAC2 which feeds PS via the LEIR.

The next machine in the chain is the Super Proton Synchrotron (SPS), the second-largest machine in CERN's accelerator complex, measuring nearly 7 km in circumference. It accelerates the bunches of protons to 450 GeV and provide beams for the Large Hadron Collider, the NA61/SHINE, the NA62 and the COMPASS experiments. It is a cycling machine, with the cycles having a period of about 10 s and it includes 1317 conventional (room-temperature) electromagnets, including 744 dipoles to bend the beams round the ring. The transverse beam size is largest at injection and decreases with the square root of the beam energy during acceleration. When the SPS operates as LHC injector, up to 288 bunches are accelerated, each bunch with about  $1.1 \times 10^{11}$  protons. The bunch length is 0.5~ns and two neighboring bunches are separated by 25 ns so that the duration of the entire beam is about  $7~\mu s$  [4].

Ions are generated in the *Lead LINAC* (LINAC3), however, they do not pass via the PSB, but instead are injected, accumulated and accelerated in the Low Energy Ion Ring (LEIR). From this accumulator, the ions are transferred to the PS, and then they follow the proton route [5].

The Cern Control Center (CCC) controls this extensive process by joining all of the accelerator operators with the engineering and cryogenics departments. By coordinating the process of

injection, the CCC guarantees a high-quality beam.

### 2.2 Luminocity of the LHC

Once the proton beams have reached nominal energies and have acquired stabilised orbits inside the LHC ring, they are brought to collision in the four Interaction Points (IPs) at which the detectors are positioned. The rate of a certain event  $R_{event}$  for a given interaction with cross-section,  $\sigma_{event}$ , is defined as

$$R_{event} = \mathcal{L}\sigma_{event},$$

(2.1)

where  $\mathcal{L}$  is the instantaneous luminosity for two oppositely directed beams. This instantaneous luminosity only depends on the beam parameters and can be written as

$$\mathcal{L} \equiv f_{rev} \frac{N_1 N_2}{4\pi \sigma_x \sigma_y}.$$

(2.2)

where  $\mathcal{L}$  is the *instantaneous luminosity* for two oppositely directed beams of relativistic particles with *revolution frequency*  $f_{rev}$ . The terms  $N_1$  and  $N_2$  are the number of protons within the two beam bunches. The quantity  $4\pi\sigma_x\sigma_y$  is the *effective section* of collision that depends on the cross section of the bunch ("effective" because the beam profile doesn't have a sharp edge).

We can also express the Luminosity in terms of  $\epsilon$  (*emittance*) and  $\beta$  (*amplitude function*) as

$$\mathcal{L} = f_{rev} \frac{N_1 N_2}{4\pi\epsilon\beta^*}.$$

(2.3)

The transverse emittance,  $\epsilon$ , and the amplitude function,  $\beta$ , both express the beam size. A low emittance particle beam is a beam where the particles are confined to a small distance and have nearly the same momentum. The amplitude function at the IP,  $\beta^*$ , is determined by the accelerator's magnet configuration (basically, the quadrupole magnet arrangement) and powering. If  $\beta^*$  is low, the beam is narrower, "squeezed", while if  $\beta^*$  is high, the beam is wide and straight. Clearly it is desired  $\beta^*$  to be as small as possible. How small depends on the capability of the hardware to make a near-focus at the IP. It can be deduced that the LHC peak luminosity is constrained by the machine's ability to make high population bunches of low emittance to collide at high frequency at locations where the beam optics provide as low values of the amplitude functions as possible.

The integral of the delivered luminosity over time is called *Integrated Luminosity*. It is a measurement of the collected data size, and it is an important value to characterize the performance of an accelerator because it directly relates to the number of observed events. The integral (Equation 2.4) is taken over the *sensitive time*, i.e., excluding possible dead time:

$$L = \int \mathcal{L}dt. \tag{2.4}$$

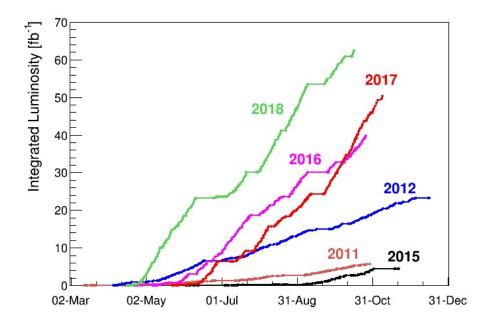

It is expressed in inverse cross section. The next graph shows the integrated luminosity delivered to the ATLAS and CMS experiments during different LHC runs. The 2018 run produced 65  $fb^{-1}$  of data, which is 16  $fb^{-1}$  more than in 2017 (Figure 2.2).

**Figure 2.2:** Integrated luminosity delivered to the ATLAS and CMS experiments during different LHC runs (Image: CERN).

The luminosity in the LHC is not constant over a physics run, but decays due to the degradation of intensities and emittances of the circulating beams. The main cause of the luminosity decay during nominal LHC operation is the beam loss from collisions. The decay of the beam intensity and luminosity as functions of time is given by:

$$\mathcal{L} = \frac{\mathcal{L}_0}{(1 + \frac{t}{\tau_{nuclear}})^2} \tag{2.5}$$

where  $\mathcal{L}_0$  is the *initial luminosity* and  $\tau_{nuclear}$  is the *initial decay time* of the bunch intensity due to beam collisions. The time required to reach 1/e of the initial luminosity is  $\tau_{nuclear,1/e} \approx 29 \ h$ .

Other contributions to beam losses come from *Touschek scattering* and from particle losses due to a slow emittance blow-up. Emittance blow-up can be caused by the scattering of particles

on residual gas, the nonlinear force of the beam-beam interaction, RF noise and IBS scattering effects. Approximating further the decay by an exponential process, the net luminosity lifetime can be estimated as:

$$\frac{1}{\tau_L} = \frac{1}{\tau_{IBS}} + \frac{1}{\tau_{restgas}} + \frac{1}{\tau_{nuclear,1/e}} \tag{2.6}$$

Integrating the luminosity over one run yields:

$$L = L_0 \tau_L [1 - e^{-T_{RUN}/\tau^L}] \tag{2.7}$$

where  $T_{run}$  is the *total length* of the luminosity run. The overall collider efficiency depends on the ratio of the length of the run to the average turnaround time [4].

### 2.3 LHC experiments

Seven experiments, at the Large Hadron Collider, use detectors to analyze particles produced by collisions in the accelerator. CMS, ATLAS, ALICE, LHCb, TOTEM, LHCf and MoEDAL are run by collaborations of scientists from institutes all over the world. Each experiment is distinct, and characterized by its detectors.

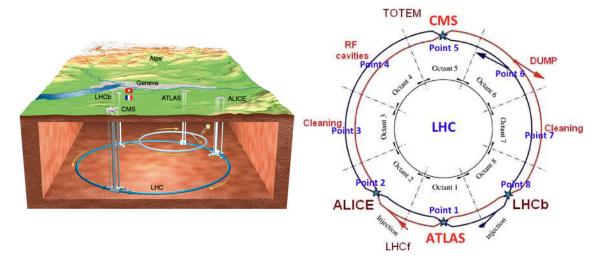

**Figure 2.3: LEFT:** A map of the LHC with the four bigger experiments. **RIGHT:** Layout of the LHC, showing separation into octants, with beam-1 (beam-2) rotating clockwise (anti-clockwise). The four large experiments, the beam injection points, the RF-cavities location, the beam cleaning and the dump locations are shown (taken from [6]).

- ▶ CMS is one of the two general-purpose detectors with the purpose of investigating the largest range of physics possible. Its broad physics program ranges from studying the *Standard Model* (including the Higgs boson) to searching for extra dimensions and particles that could make up dark matter. Built around a huge solenoid magnet that generates a field of 4 T, it was constructed in 15 sections at ground level, before being lowered and reassembled into an underground cavern, near the french village of Cessy. The complete detector measures 21 m long, 15 m wide and 15 m high, weighting more than 14,000 ton.

- ▶ ATLAS is the second general-purpose particle physics experiment and, together with CMS, is designed to exploit the full discovery potential and the huge range of physics opportunities that the LHC provides. As with CMS, ATLAS 's scientific exploration uses precision measurements to test the predictions of the *Standard Model* which encapsulates our current understanding of what the building blocks of matter are and how they interact.

- ▶ ALICE experiment is optimized to study heavy-ion (Pb-Pb nuclei) collisions at a centre of mass energy of 2.76 TeV per nucleon pair. The high temperature and energy density produce *quark-gluon plasma* in conditions similar to the ones existed a fraction of the second after the *Big Bang*, before quarks and gluons bound together to form hadrons and heavier particles. The existence of the quark-gluon plasma and its properties are key issues in *quantum chromodynamics* for understanding color confinement and chiral symmetry restoration [7].

- ▶ LHCb is an experiment dedicated to heavy flavour physics. Its primary goal is to look for indirect evidence of new physics in cp violation and rare decays of beauty and charm hadrons. The experiment allows physicists to study cp violation and rare decays of  $B_d$ ,  $B_s$  and D-mesons with high statistics and using many different decay modes [8].

- ▶ **TOTEM** is an independent experiment, but technically integrated into CMS. Its main purpose is to measure the total p-p cross section, with a method independent of the luminosity, and study elastic diffractive scattering. It consists of two tracking telescopes, installed on each side of pseudo-rapidity region  $3.1 \le |\eta| \le 6.5$  and *Roman Pot* stations placed at distances of  $\pm$  147 m and  $\pm$  220 m from the CMS interaction Point (P5) [9].

- ▶ LHCf is intended to measure the energy and numbers of *neutral pions* ( $\pi_0$ ) produced by the collider, in an effort to explain the origin of ultra-high-energy cosmic rays. It consists of two similar calorimeters placed symmetrically, at a distance of 140 m from the ATLAS Interaction Point, covering the very forward region of the LHC [10].

- ▶ MoEDAL is designed to enhance, in a complementary way, the physics reach of the LHC. The prime motivation of MoEDAL is to directly search for the Magnetic Mono-pole and other highly ionizing Stable (or pseudo-stable) Massive Particles (SMPs) at the LHC. MoEDAL is using a passive plastic track technique which does not require a trigger. It is, thus, optimized to detect slow moving particles that the main LHC experiments cannot detect due to the very short LHC trigger window of 25 ns. [11]

### 2.4 The High Luminocity LHC upgrade

The commissioning of the Large Hadron Collider marked the beginning of a remarkable era for cosmology, astrophysics and high energy physics. It is since then, at the forefront of attempts to understand the fundamental nature of the universe. The discovery of the Higgs boson in 2012 was a major milestone in the history of science, but beyond this, the LHC has the potential to go on and help answer some key questions; the existence of super-symmetry, the nature of dark matter, the existence of extra dimensions and the properties of the Higgs boson are some of the most important of them. To extend its discovery potential, the world's most powerful accelerator has to be upgraded.

In the 2020s, the LHC will go through major upgrade to extend its operability by another decade and to increase its luminosity (and thus collision rate) by a factor of five, beyond its initial design value. The Integrated Luminosity design goal is an increase by a factor of ten. The necessary developments require about 10 years to prototype, test and realize new equipment. The updated machine configuration, the so-called HL-LHC, will rely on a number of key innovative technologies representing exceptional technological challenges.

Figure 2.4: LHC baseline plan showing the collisions energy (upper red line) and luminosity (lower green lines). The first long shutdown (LS1) in 2013-2014 allowed the design parameters of beam energy and luminosity to be reached. The second long shutdown (LS2) in 2018-2019, will consolidate luminosity and reliability as well as the upgrading of the LHC injectors. After LS3 (2023-2025), the machine will be in the High Luminosity configuration (HL-LHC)[12].

In spring 2016, the CERN Council approved the proposal, describing the goals of the upgrade, the physics case and the technology challenges of the HL-LHC. This proposal [13] covers all the project period including installation and commissioning by 2026 [12]. The main objective of the HL-LHC design study was to determine a set of beam parameters and the hardware configuration that will enable the LHC to reach the following targets:

▶ a peak luminosity of  $5 \times 10^{34} \ cm^{-2} s^{-1}$  with levelling, and

▶ an integrated luminosity of  $250fb^{-1}$  per year with the goal of  $3000fb^{-1}$  in 10-12 years after the upgrade.

Regarding the hardware, several systems need to be improved, and possibly replaced, to allow the LHC machine to achieve luminosity above the current ultimate peak luminosity of  $2 \times 10^{34}~cm^{-2}s^{-1}$ . The main hardware upgrades required are:

- ▶ Inner triplet magnets. Possible radiation damage to the triplet quadrupoles could cause sudden electric breakdown, entailing serious and long repairs. Replacement of the low-beta triplet is a long intervention, requiring a one- to two-year shutdown and must be coupled with major detector upgrades.

- ► Cryogenics. The installation of a new cryogenics plant that will allow full separation between superconducting rf and magnet cooling is planned. This will increase intervention flexibility and machine availability.

- ▶ Collimation. The collimation system will require an upgrade that takes into account the need for the lower impedance imposed by the planned increased beam intensities. A new configuration will also be required to protect the new triplets.

- ▶ Electronics boards of the power converter system. Considerable effort is being made to study how to replace the radiation-sensitive electronics boards of the power converter system with radiation-hard cards.

- ▶ Quench Protection System(QPS)), machine protection and remote manipulation.

- QPS for the superconducting magnets is based on a design that is almost 20 years old.

- Machine protection will require improvement.

- Remote manipulation While full robotics is difficult to implement, given the conditions on the ground, remote manipulation, enhanced reality and supervision are the keys to minimize the radiation doses sustained during interventions.

#### 2.4.1 The HL-LHC luminocity

As already mentioned, the major upgrade of the LHC will allow us to push the machine peak levelled luminosity to about  $5 \times 10^{34}~cm^{-2}s^{-1}$ , while the *pile-up* (number of events per bunch crossing) will increase to around 200. This luminosity level should enable the collection of up to  $300-350~fb^{-1}$  per year, provided that the experiments can digest this pile-up level. The luminosity profile without levelling, however, quickly decreases from the initial peak value due to "luminosity burn-off". A further limitation upon peak luminosity is imposed by the consideration of energy deposition by collision debris in the interaction region magnets, and the necessity to limit the peak pile-up in the experimental detector.

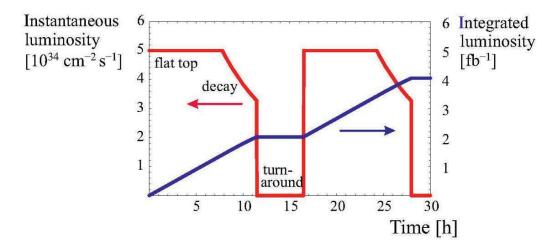

These considerations lead to a luminosity profile with optimized run time and levelling at  $\approx 5 \times 10^{34}~cm^{-2}s^{-1}$ ) (Figure 2.5). The average luminosity achieved with levelling is almost the same as that without levelling in an ideal running configuration without premature fill aborts. In terms of total integrated luminosity, the ultimate performance corresponds to a value of about  $4000~fb^{-1}$ .

Figure 2.5: Luminosity cycle for HL-LHC with levelling and a short decay (optimized for integrated luminosity)[12].

## Chapter 3

# The CMS experiment

The Compact Muon Solenoid detector is one of the two large multi-purpose detectors operating at the LHC at CERN. It is installed 100 m underground, at Interaction Point 5 (P5), outside of the French village of Cessy, between Lake Geneva and the Jura mountains. It has a broad physics program, ranging from studying the Standard Model, to searching for extra dimensions and particles that could make up dark matter. Great emphasis, however, has been given to the discovery of the Higgs boson, due to its key role in understanding the nature of the electroweak symmetry breaking. The experimental study of the Higgs mechanism, can also shed light on the mathematical consistency of the Standard Model at energy scales above 1 TeV.

The unique conditions of the LHC require a very careful design of the detectors. At the design luminosity, a mean of about 20 inelastic collisions is superimposed on the event of interest. This implies that around 1000 charged particles emerge from the interaction region every 25 ns. The products of an interaction under study may be mixed with products from other interactions in the same bunch crossing. This problem, clearly, becomes more severe when the response time of a detector element and its electronic signal is longer than 25 ns. This effect is called pile-up and can be reduced by using high-granularity detectors with good time resolution, resulting in low occupancy. This requires the use of millions of detector electronic channels with very good synchronization. CMS detector observes an event rate of approximately  $10^9$  inelastic events per second, which leads to a number of experimental challenges. The online event selection process (trigger) must reduce the huge rate to about 1000 events per second for storage and subsequent analysis.

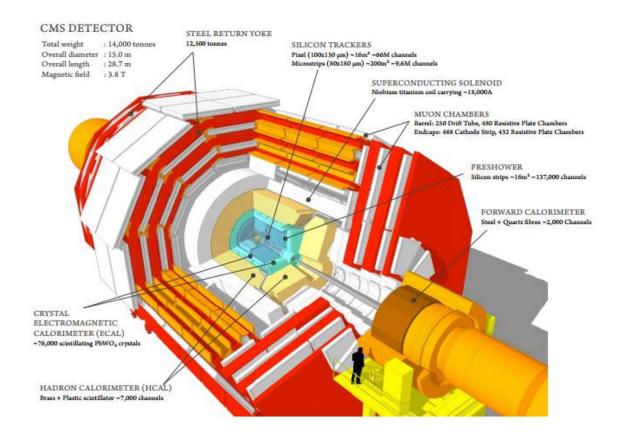

The CMS detector, as can be seen in Figure 3.1, houses a high-magnetic field created by a large-bore superconducting solenoid, surrounding a silicon pixel and strip tracker, an electromagnetic calorimeter and a sampling hadron calorimeter. The iron yoke of the flux-return is instrumented with four stations of muon detectors, covering most of the  $4\pi$  solid angle. Forward sampling calorimeters extend the pseudorapidity coverage to high values ( $|\eta| < 5$ ), assuring good hermeticity and stereoscopic coverage. The overall dimensions of the CMS detector are a length

Figure 3.1: A cutaway view of the CMS detector [14].

of 21.6 m, a diameter of 14.6 m and a total weight of 12.5 kton.

The CMS detector requirements, in order to meet the goals of the LHC physics program, can be summarised as follows:

- ▶ Good muon identification and momentum resolution over a wide range of momenta and angles, a good di-muon mass resolution ( $\sim$ 1% at 100 GeV), and the ability to determine, unambiguously, the muons charge with p < 1 TeV.

- ▶ Good momentum resolution and reconstruction efficiency in the inner tracker for charged particles. Efficient triggering and offline tagging of  $\tau$ -particles and b-jets, which implies the use of pixel detectors close to the interaction region.

- ▶ Good electromagnetic energy resolution, good di-photon and di-electron mass resolution ( $\sim 1\%$  at 100 GeV), wide geometric coverage,  $\pi^0$  rejection, and efficient photon and lepton isolation at high luminosity.

- ▶ Good *missing transverse energy* and di-jet mass resolution, which requires the use of hadron calorimeters with large hermetic geometric coverage and with fine lateral segmentation.

### 3.1 The CMS Coordinate system

In the CMS coordinate system, the origin is centered at the nominal collision point, inside the experiment, the y-axis pointing vertically upwards, and the x-axis pointing radially inwards toward the center of the LHC. Thus, the z-axis points along the beam direction toward the Jura mountains from LHC Point 5. The azimuthal angle  $\phi$  is measured from the x-axis in the x-y plane. The polar angle,  $\theta$ , is measured from the z-axis. The pseudorapidity,  $\eta$ , is defined as:

$$\eta = -\ln\tan(\frac{\theta}{2}). \tag{3.1}$$

The momentum and energy measured transverse to the beam direction, denoted by  $p_T$  and  $E_T$ , respectively, are computed from the x and y components. The imbalance of energy measured in the transverse plane equals to the missing transverse energy and it is denoted by  $E_T^{miss}$ .

### 3.2 The superconducting solenoid magnet

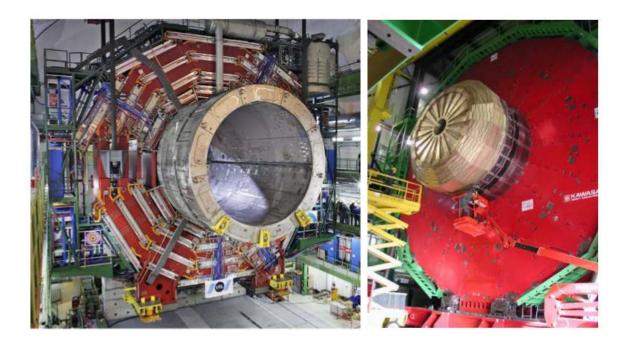

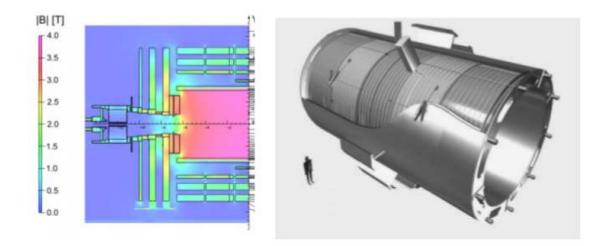

As highlighted before, it is crucial for the CMS to identify muons and in general charged particles with good momentum and efficiency. To achieve these goals and measure precisely the momentum of energetic charged particles, large bending power is required. This scale of bending power can only be achieved with the use of superconducting magnets. The superconducting magnet of the CMS detector has been designed to reach a 4 T field in a free bore of 6 m diameter and 12.5 m length with a stored energy of 2.6 GJ at full current. The flux is returned through a 10,000 ton yoke, comprising of 5 wheels for the barrel region and 2 endcaps composed of three disks each (Figure 3.2 and Figure 3.3).

The distinctive feature of the 220 ton cold mass is the 4-layer winding, made from a stabilised, reinforced NbTi conductor. The ratio between stored energy and cold mass is high (11.6 kJ/kg), causing a large mechanical deformation ( $\sim$ 0.15%) during energising, well beyond the values of previous solenoidal detector magnets.

The single most important aspect of the overall detector design is the configuration and parameters of the magnetic field for the measurement of muon momenta. The parameters of the CMS magnet are summarised in Table 3.1. The magnet was assembled and tested in a surface hall (SX5), prior to being lowered 90 m below ground to its final position in the experimental cavern. After provisional connection to its ancillaries, the CMS magnet, was fully and successfully tested and commissioned in SX5 by the end of autumn 2006.

| General parameters                           |                           |

|----------------------------------------------|---------------------------|

| Magnetic length                              | 12.5 m                    |

| Cold bore diameter                           | 6.3 m                     |

| Central magnetic Induction                   | 4 T                       |

| Total Ampere-turns                           | 41.7 MA-turns             |

| Nominal current                              | 19.14 kA                  |

| Inductance                                   | 14.2 H                    |

| Stored energy                                | 2.6 GJ                    |

| Cold Mass                                    |                           |

| Layout                                       | Five modules mechanically |

|                                              | and electrically coupled  |

| Radial thickness of cold mass                | 312 mm                    |

| Radiation thickness of cold mass             | Weight of cold mass       |

| Weight of cold mass                          | 220 t                     |

| Maximum induction on conductor               | 4.6 T                     |

| Temperature margin wrt operating temperature | 1.8 T                     |

| Stored energy/unit cold mass                 | 11.6 kJ/kg                |

| Iron yoke                                    |                           |

| Outer diameter of the iron yoke              | 14 m                      |

| Lenght of barrel                             | 13 m                      |

| Thickness of the iron layers in barrel       | 300, 630 mm               |

| Mass of iron in barrel                       | 6000 t                    |

| Thickness of iron disks in endcaps           | 250, 600 and 600 mm       |

| Mass of iron in each endcap                  | 2000 t                    |

| Total mass of iron in return yoke            | 10 000 t                  |

Table 3.1: Main parameters of the CMS magnet

**Figure 3.2: LEFT:** The Compact Muon Solenoid magnet and one of the five barrel yoke wheels. **RIGHT:** View of one endcap disk (out of six), 15 m in diameter. This 600 mm thick disk, weighing 700 ton, is supporting a 300 ton hadronic endcap calorimeter

Figure 3.3: LEFT: Value of |B| predicted on a longitudinal section of the CMS detector for the underground model at a central magnetic flux density of 3.8 T [15]. RIGHT: Perspective view of the CMS coil inside the outer vacuum tank showing the five modules, the tie-bar suspension system, and the thermosyphon cooling circuits outside the mandrels [16].

### 3.3 The Inner Tracking System Overview

The inner tracking system is the innermost part of the CMS detector. It is designed to provide a precise and efficient measurement of the trajectories of charged particles emerging from the LHC collisions. It is very important, for the tracking system, to distinguish primary and secondary vertices  $^1$ . Furthermore, determining precisely the secondary vertices and the impact parameters  $d_{xy}$  and  $d_z$ , is required for the efficient identification of heavy flavours.

The inner tracking system surrounds the thin beryllium beam-pipe which accommodates the LHC vacuum and is centred at the IP where the two beams collide. Its total tracking volume is given by a cylinder of 5.8 m length and 2.6 m diameter. The CMS solenoid provides a homogeneous magnetic field of 4 T over the full volume of the tracker.

During the development phase of the tracker system, it was calculated that for the LHC design luminosity of  $1\times 10^{34}~cm^{-2}s^{-1}$ , an average of about 1000 charged particles, that originate from more than 20 overlapping proton-proton interactions, would be produced every 25 ns. The inner tracker is the closest system to the interaction point and is subjected to an enormous particle flux. Therefore, a detector technology featuring high granularity and fast response was selected. The high granularity insures that the trajectories can be identified reliably, and the detector's fast response the trajectory's assignment to the correct bunch crossing. The expected tracker hit rate density was 100 MHz/cm² in the barrel part, at a radius of 4 cm. This requires high power on-detector electronics and an efficient cooling system. A compromise was made, however, to keeping the amount of tracker material to as little as possible, to minimise phenomena such as multiple scattering, bremsstrahlung, photon conversion and nuclear interactions.

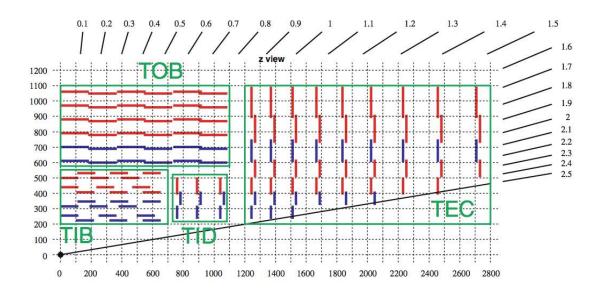

#### 3.3.1 The Silicon Strip Tracker

The CMS Silicon Strip Tracker (SST), together with the pixel detector, provides measurement of the charged particle trajectories up to a pseudorapidity of  $|\eta| < 2.5$ . The layout of the SST is shown in Figure 3.4. The detector is 5 m long with a diameter of 2.5 m, and it is segmented into 9.6 million single-sided *p-on-n* micro-strip sensors, distributed over 15148 modules. They provide 198  $m^2$  of active silicon area.

The barrel region consists of 10 layers, with 4 layers in the Tracker Inner Barrel (TIB) and 6 layers in the Tracker Outer Barrel (TOB). In the forward region, the detector consists of two Tracker End-Cap (TEC) composed of 7 rings each, as shown in Figure 3.4. Stereo modules constructed from two silicon modules, glued back-to-back with their strips aligned at an angle of 100 mrad, are used in 4 layers of the barrel and 3 disks of the endcap, to provide the 2D measurements. The APV25 chip was designed for the readout of the silicon microstrip detector. It is a 128-channel analogue pipeline chip, developed to meet the demands of low-noise, low power and radiation hardness. Each channel comprises a low noise amplifier, a 192 cell analogue pipeline

<sup>&</sup>lt;sup>1</sup>The point of decay of a collision product that was itself produced in the primary vertex

and a de-convolution readout circuit. Output data are transmitted on a single differential output via an analogue multiplexer [17]. They are then converted to optical signals on analog-optohybrids (AOH), and transmitted to Front-End Drivers (FEDs), located in the service cavern outside the radiation zone, via optical fibers. Pedestal and common mode subtraction, as well as cluster finding, are performed in the FEDs. Clock and trigger information is distributed by Front-End Controllers (FECs) to Communication and Control Units (CCU) grouped in token ring networks (control rings).

Figure 3.4: The layout of the CMS Silicon Strip Tracker [18].

The CMS Silicon Strip Tracker has shown no significant degradation after 10 years of operation, and it continues to deliver high quality data for physics analyses. At the beginning of 2018 the operational temperature of the detector has been changed from -15°C to -20°C, which helped to decrease the leakage current in regions with degraded cooling. The detector was recalibrated and commissioned at the new operational temperature.

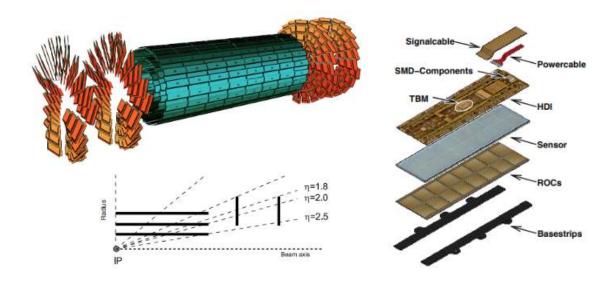

#### 3.3.2 The Pixel Detector

The pixel detector is the part of the tracking system that is closest to the interaction region. It is essential for the reconstruction of secondary vertices from b and  $\tau$  decays, and forming seed tracks for the outer track reconstruction and high level triggering. The tracks reconstructed, with the pixel detector alone, is the only available tracking information at the first stage of the High Level Trigger (HLT). In this stage, speed is more important than accuracy or efficiency. Pixel-only tracks can be reconstructed in less than 20 ms (110 ms) per event for regional (global) track finder.

The pixel detector covers a pseudorapidity range of  $|\eta| < 2.5$ , matching the acceptance of

the central tracker. The Barrel Pixel (BPix) consists of three layers and the Forward Pixel (FPix) (endcap) of two disks on each side. The BPix layers are 53 cm long and located at mean radii of 4.4, 7.3 and 10.2 cm respectively, covering an area of 0.78  $m^2$ . The FPix disks are placed on each side of the interaction point at  $z=\pm 34.5$  cm and  $z=\pm 46.5$  cm, extending from 6 to 15 cm in radius, covering an area of another 0.28  $m^2$ . The total amount of pixels is 66 million, 48 millions contained in the Barrel Pixel and 18 millions in the Forward Pixel, with a pixel unit cell of  $100\mu m \times 150\mu m$ . This very fine granularity is important to avoid saturation and keep the tracker occupancy at the level of  $\sim$ 1%, due to the high hit-rate density at very small distances around the Interaction Point. The geometric arrangement of the 3 barrel layers and the forward pixel disks (as shown in Figure 3.5) gives 3 tracking points over almost the full  $\eta$ -range. In the high  $\eta$  region the two disk points are combined with the lowest possible radius point from the 4.4 cm barrel layer.

Figure 3.5: LEFT: Sketch (top) and geometrical layout (bottom) of the pixel detector. RIGHT: Exploded view of a barrel module (taken from [19], [20]).

The barrel layers are made out of two types of sensor modules, half modules and full modules. The three layers comprise of 128, 224 and 320 full modules respectively and 32 half modules each at the edges of the half-shells. The barrel module sensor is a pixelated, high dose, n implantation in a lightly n-doped bulk material. The backside is p-doped forming the n junction. The active area of a full (half) module sensor is  $64.8mm \times 5.3mm$ . It is a double sided processed "n+ on n" design. The inter-pixel isolation is done with a moderated p-spray technique. For the forward pixel the sensor design is of "n+ on n-" type. A p-stop isolation technique, in which a high dose p-implant surrounds each n+ type region, provides explicit electrical isolation between neighboring n+ electrodes.

Sixteen (eight) Read-Out Chips (ROCs) are bump-bonded to each full (half) sensor. The ROCs were fabricated in a commercial  $0.25~\mu m$  five-metal-layered CMOS process. Their main purposes are amplification and buffering of the charge signal from the sensor, zero suppression in the pixel unit cell, level-1 trigger verification, sending hit information and configuration data out to the Token Bit Manager (TBM) chip and adjusting various voltage levels and offsets in order to

compensate for chip-to-chip variations in the CMOS device parameters. The module is read out in a daisy chain scheme. The read out process is controlled by the TBM chip. For each level 1 trigger the TBM generates a token bit which controls 8 or 16 ROCs. One ROC at a time sends its hit information through a Low Voltage Differential Signal (LVDS) cable to the TBM chip where they are amplified and converted into a Low Current Differential Signal (LCDS). ([21], [22]). The fact that charge sharing is enhanced between pixels, due to Lorentz drift in the 4 T magnetic field, leads to increased spatial resolution through analog signal interpolation.

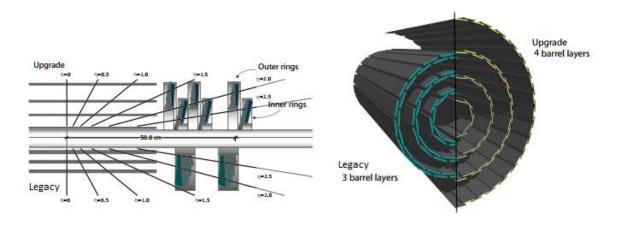

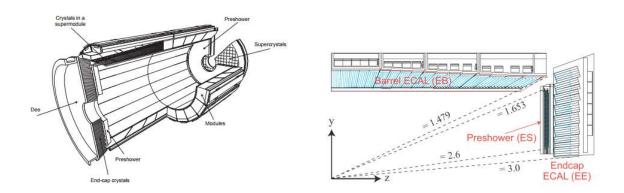

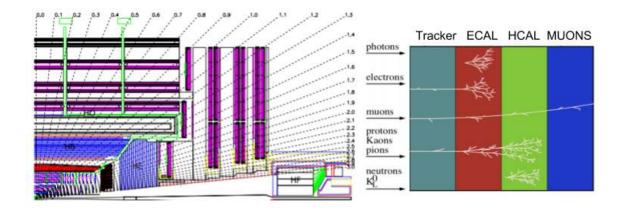

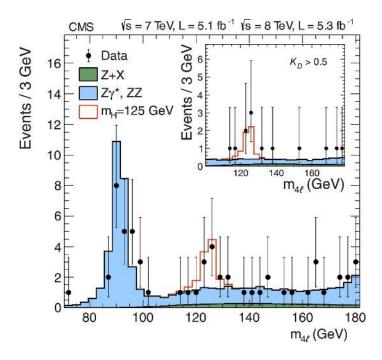

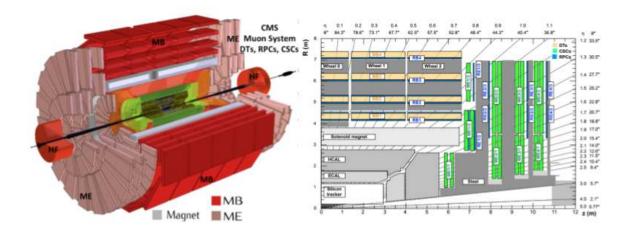

The pixel readout electronics were designed and optimized for the data rates and pixel occupancy expected for the LHC design luminosity of  $1\times 10^{34}~cm^{-2}s^{-1}$ , with 25 ns bunch spacing. For these conditions, there is a dynamic inefficiency of  $\sim 4\%$  from the current readout chip, in the innermost layer. At the nominal readout rate of 100 kHz, the data loss would have increased to 16% in the innermost layer as the luminosity went up to  $2\times 10^{34}cm^{-2}s^{-1}$ . To avoid this degradation and maintain the excellent performance of the pixel detector at higher luminosity and pile-up, the pixel detector was replaced during the year-end technical stop of 2016/2017. The old 3-layer barrel / 2-disk endcap system was replaced with a 4-layer barrel / 3-disk endcap system, providing four hit coverage (Figure 3.6). The addition of the fourth barrel layer at a radius of 16 cm, provides redundancy in pattern recognition and reduces fake rates with high pile-up. Moreover, the mass of the new detector was significantly lowered by relocating much of the passive material out of the tracking volume.